| (8 intermediate revisions by the same user not shown) | |||

| Line 28: | Line 28: | ||

|isa family=x86 | |isa family=x86 | ||

|microarch=Raptor Lake | |microarch=Raptor Lake | ||

| + | |microarch 2=Raptor Cove | ||

| + | |microarch 3=Gracemont | ||

|chipset=700 series | |chipset=700 series | ||

|core name=Raptor Lake S | |core name=Raptor Lake S | ||

| Line 48: | Line 50: | ||

|predecessor link=intel/core_i5/i5-12600kf | |predecessor link=intel/core_i5/i5-12600kf | ||

}} | }} | ||

| + | '''Core i5-13600KF''' is a {{arch|64}} [[tetradeca-core]] high-end performance [[x86]] desktop microprocessor introduced by [[Intel]] in late [[2022]]. This processor, which is based on the {{intel|Raptor Lake|l=arch}} microarchitecture, is manufactured on Intel's enhanced [[Intel 7]] process. The i5-13600KF is a [[heterogeneous multicore]] SoC integrating eight [[big core|big]] {{intel|Raptor Cove|l=arch}} cores along with sixteen [[small core|small]] {{intel|Gracemont|l=arch}} cores. The [[big cores]] operate at 3.5 GHz with a {{intel|Turbo Boost}} frequency of up to 5.1 GHz. The [[small cores]] operate at 2.6 GHz with a {{intel|Turbo Boost}} frequency of up to 3.9 GHz. This processor has a base power of 125 W and a maximum turbo power of 181 W. This chip supports up to 128 GiB of dual-channel DDR5-5600 memory. This chip does not incorporate any integrated graphics. | ||

| + | |||

| + | The {{\\|i5-13600K}} is an identical version of this chip with integrated graphics. | ||

| + | |||

| + | == Cache == | ||

| + | {{main|intel/microarchitectures/raptor_lake#Memory_Hierarchy|l1=Raptor Lake § Cache}} | ||

| + | This processor features 30 MiB of [[L3 cache]] shared among all the [[big cores]] and all the [[small core]] clusters. | ||

| + | |||

| + | === Small Core === | ||

| + | {{main|intel/microarchitectures/gracemont#Memory_Hierarchy|l1=Gracemont § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=768 KiB | ||

| + | |l1i cache=512 MiB | ||

| + | |l1i break=8x64 KiB | ||

| + | |l1d cache=256 KiB | ||

| + | |l1d break=8x32 KiB | ||

| + | |l2 cache=8 MiB | ||

| + | |l2 break=2x4 MiB | ||

| + | |l3 cache=6 MiB | ||

| + | |l3 break=2x3 MiB | ||

| + | }} | ||

| + | |||

| + | === Big Core === | ||

| + | {{main|intel/microarchitectures/raptor cove#Memory_Hierarchy|l1=Raptor Cove § Cache}} | ||

| + | {{cache size | ||

| + | |l1 cache=480 KiB | ||

| + | |l1i cache=192 KiB | ||

| + | |l1i break=6x32 KiB | ||

| + | |l1d cache=288 KiB | ||

| + | |l1d break=6x48 KiB | ||

| + | |l2 cache=12 MiB | ||

| + | |l2 break=6x2 MiB | ||

| + | |l3 cache=18 MiB | ||

| + | |l3 break=6x3 MiB | ||

| + | }} | ||

| + | |||

| + | == Memory controller == | ||

| + | {{memory controller | ||

| + | |type=DDR5-5600 | ||

| + | |type 2=DDR4-3200 | ||

| + | |ecc=No | ||

| + | |max mem=128 GiB | ||

| + | |controllers=1 | ||

| + | |channels=2 | ||

| + | |max bandwidth=83.45 GiB/s | ||

| + | |bandwidth schan=41.72 GiB/s | ||

| + | |bandwidth dchan=83.45 GiB/s | ||

| + | }} | ||

| + | |||

| + | == Expansions == | ||

| + | {{expansions main | ||

| + | | | ||

| + | {{expansions entry | ||

| + | |type=PCIe | ||

| + | |pcie revision=5.0 | ||

| + | |pcie lanes=16 | ||

| + | |pcie config=1x16 | ||

| + | |pcie config 2=2x8 | ||

| + | }} | ||

| + | {{expansions entry | ||

| + | |type=PCIe | ||

| + | |pcie revision=4.0 | ||

| + | |pcie lanes=4 | ||

| + | |pcie config=1x4 | ||

| + | }} | ||

| + | }} | ||

| + | |||

| + | == Features == | ||

| + | {{x86 features | ||

| + | |real=Yes | ||

| + | |protected=Yes | ||

| + | |smm=Yes | ||

| + | |fpu=Yes | ||

| + | |x8616=Yes | ||

| + | |x8632=Yes | ||

| + | |x8664=Yes | ||

| + | |nx=Yes | ||

| + | |mmx=Yes | ||

| + | |emmx=Yes | ||

| + | |sse=Yes | ||

| + | |sse2=Yes | ||

| + | |sse3=Yes | ||

| + | |ssse3=Yes | ||

| + | |sse41=Yes | ||

| + | |sse42=Yes | ||

| + | |sse4a=No | ||

| + | |sse_gfni=No | ||

| + | |avx=Yes | ||

| + | |avx_gfni=No | ||

| + | |avx2=Yes | ||

| + | |avx512f=No | ||

| + | |avx512cd=No | ||

| + | |avx512er=No | ||

| + | |avx512pf=No | ||

| + | |avx512bw=No | ||

| + | |avx512dq=No | ||

| + | |avx512vl=No | ||

| + | |avx512ifma=No | ||

| + | |avx512vbmi=No | ||

| + | |avx5124fmaps=No | ||

| + | |avx512vnni=No | ||

| + | |avx5124vnniw=No | ||

| + | |avx512vpopcntdq=No | ||

| + | |avx512gfni=No | ||

| + | |avx512vaes=No | ||

| + | |avx512vbmi2=No | ||

| + | |avx512bitalg=No | ||

| + | |avx512vpclmulqdq=No | ||

| + | |abm=Yes | ||

| + | |tbm=No | ||

| + | |bmi1=Yes | ||

| + | |bmi2=Yes | ||

| + | |fma3=Yes | ||

| + | |fma4=No | ||

| + | |aes=Yes | ||

| + | |rdrand=Yes | ||

| + | |sha=No | ||

| + | |xop=No | ||

| + | |adx=Yes | ||

| + | |clmul=Yes | ||

| + | |f16c=Yes | ||

| + | |bfloat16=No | ||

| + | |tbt1=No | ||

| + | |tbt2=Yes | ||

| + | |tbmt3=No | ||

| + | |tvb=No | ||

| + | |bpt=No | ||

| + | |eist=Yes | ||

| + | |sst=Yes | ||

| + | |flex=No | ||

| + | |fastmem=No | ||

| + | |ivmd=Yes | ||

| + | |intelnodecontroller=No | ||

| + | |intelnode=No | ||

| + | |kpt=No | ||

| + | |tme=Yes | ||

| + | |mktme=Yes | ||

| + | |ptt=No | ||

| + | |intelrunsure=No | ||

| + | |mbe=Yes | ||

| + | |isrt=No | ||

| + | |sba=No | ||

| + | |mwt=No | ||

| + | |sipp=No | ||

| + | |att=No | ||

| + | |ipt=No | ||

| + | |tsx=No | ||

| + | |txt=No | ||

| + | |ht=Yes | ||

| + | |vpro=Yes | ||

| + | |vtx=Yes | ||

| + | |vtd=Yes | ||

| + | |ept=Yes | ||

| + | |mpx=No | ||

| + | |sgx=No | ||

| + | |securekey=Yes | ||

| + | |osguard=Yes | ||

| + | |intqat=No | ||

| + | |dlboost=Yes | ||

| + | |3dnow=No | ||

| + | |e3dnow=No | ||

| + | |smartmp=No | ||

| + | |powernow=No | ||

| + | |amdvi=No | ||

| + | |amdv=No | ||

| + | |amdsme=No | ||

| + | |amdtsme=No | ||

| + | |amdsev=No | ||

| + | |rvi=No | ||

| + | |smt=No | ||

| + | |sensemi=No | ||

| + | |xfr=No | ||

| + | |xfr2=No | ||

| + | |mxfr=No | ||

| + | |amdpb=No | ||

| + | |amdpb2=No | ||

| + | |amdpbod=No | ||

| + | }} | ||

| + | |||

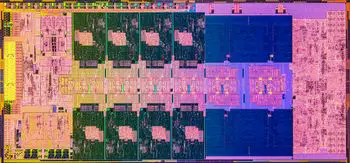

| + | == Die == | ||

| + | {{intel raptor lake die}} | ||

| + | |||

| + | == Documents == | ||

| + | * [[:File:13th-gen-processor-product-brief.pdf|Product Brief]] | ||

Latest revision as of 00:18, 3 October 2022

| Edit Values | |

| Core i5-13600KF | |

| |

| General Info | |

| Designer | Intel |

| Manufacturer | Intel |

| Model Number | i5-13600KF |

| Part Number | BX8071513600KF, CM8071504821006 |

| S-Spec | SRMBE |

| Market | Desktop, Enthusiast |

| Introduction | September 27, 2022 (announced) October 20,2022 (launched) |

| Release Price | $294.00 (tray) $304.00 (box) |

| Shop | Amazon |

| General Specs | |

| Family | Core i5 |

| Series | i5-13000 |

| Locked | No |

| Frequency | 2,600 MHz, 3,500 MHz |

| Turbo Frequency | 5,100 MHz |

| Bus type | DMI 4.0 |

| Bus rate | 4 × 16 GT/s |

| Clock multiplier | 35 |

| Microarchitecture | |

| ISA | x86-64 (x86) |

| Microarchitecture | Raptor Lake, Raptor Cove, Gracemont |

| Chipset | 700 series |

| Core Name | Raptor Lake S |

| Core Family | 6 |

| Core Model | 183 |

| Core Stepping | B0 |

| Process | Intel 7 |

| Technology | CMOS |

| MCP | No (1 dies) |

| Word Size | 64 bit |

| Cores | 14 |

| Threads | 20 |

| Max Memory | 128 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| TDP | 125 W, 181 W |

| Packaging | |

| Package | FCLGA-1700 (LGA) |

| Dimension | 45.0 mm × 37.5 mm |

| Contacts | 1700 |

| Socket | Socket V |

| Succession | |

Core i5-13600KF is a 64-bit tetradeca-core high-end performance x86 desktop microprocessor introduced by Intel in late 2022. This processor, which is based on the Raptor Lake microarchitecture, is manufactured on Intel's enhanced Intel 7 process. The i5-13600KF is a heterogeneous multicore SoC integrating eight big Raptor Cove cores along with sixteen small Gracemont cores. The big cores operate at 3.5 GHz with a Turbo Boost frequency of up to 5.1 GHz. The small cores operate at 2.6 GHz with a Turbo Boost frequency of up to 3.9 GHz. This processor has a base power of 125 W and a maximum turbo power of 181 W. This chip supports up to 128 GiB of dual-channel DDR5-5600 memory. This chip does not incorporate any integrated graphics.

The i5-13600K is an identical version of this chip with integrated graphics.

Contents

Cache[edit]

- Main article: Raptor Lake § Cache

This processor features 30 MiB of L3 cache shared among all the big cores and all the small core clusters.

Small Core[edit]

- Main article: Gracemont § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Big Core[edit]

- Main article: Raptor Cove § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions[edit]

Expansion Options |

|||||||||

|

|||||||||

Features[edit]

[Edit/Modify Supported Features]

Die[edit]

- Main article: Raptor Lake § Raptor Lake S (8P+16E) Die

Raptor Lake S microprocessors are fabricated on Intel's enhanced Intel 7 process. This SoC uses a single monolithic die which includes both the CPU cores along with the integrated GPU and various other additional components.

Documents[edit]

| full page name | intel/core i5/i5-13600kf + |

| instance of | microprocessor + |

| ldate | 1900 + |