-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Difference between revisions of "amd/zeppelin"

< amd

(zeppelin) |

|||

| Line 6: | Line 6: | ||

| − | :[[File:amd zeppelin basic block.svg|400px]] | + | :[[File:amd zeppelin basic block.svg|class=wikichip_ogimage|400px]] |

[[category:amd]] | [[category:amd]] | ||

Revision as of 19:06, 23 March 2018

Zeppelin is a scalable system on a chip designed by AMD in order to satisfy the need of multiple market segments.

Overview

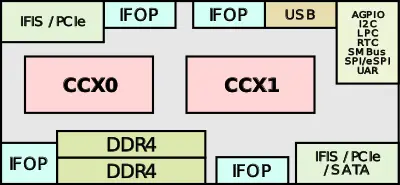

Zeppelin is an SoC designed by AMD capable of scaling from a single-die to a multi-chip package consisting of up to 4 dies interconnected together using AMD's proprietary Infinity Fabric. The die consists of two CPU Complexes, two DDR4 channels, USB, low-power I/O, and a series of IFOP and IFIS SerDes that are used to interlink multiple dies and sockets together.

Retrieved from "https://en.wikichip.org/w/index.php?title=amd/zeppelin&oldid=75460"