-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Difference between revisions of "ti/tms1000/tms1098"

Maxanco2017 (talk | contribs) (The 1098 page creation) |

(+title) |

||

| Line 1: | Line 1: | ||

| + | {{ti title|TMS1098}} | ||

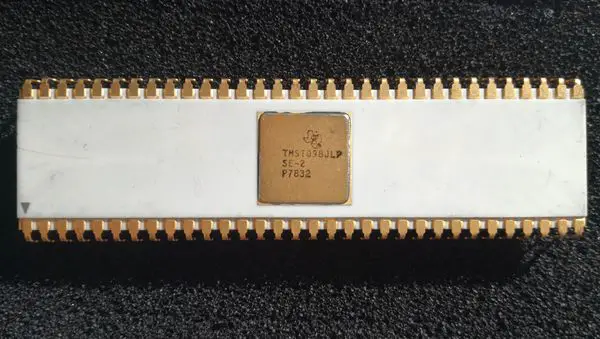

The TMS1098JL is a ROM-less version of TMS1000-TMS1200. It has 64 pins, 128x4 bits of RAM, 8 bits of "O" parallel latched data outputs and 16 "R" individually addressed output latches. The package pin count is 64. | The TMS1098JL is a ROM-less version of TMS1000-TMS1200. It has 64 pins, 128x4 bits of RAM, 8 bits of "O" parallel latched data outputs and 16 "R" individually addressed output latches. The package pin count is 64. | ||

Revision as of 13:42, 13 December 2017

The TMS1098JL is a ROM-less version of TMS1000-TMS1200. It has 64 pins, 128x4 bits of RAM, 8 bits of "O" parallel latched data outputs and 16 "R" individually addressed output latches. The package pin count is 64.

The maximum-rated voltage is 20 V and the typical dissipation is 110mW (per power supply of 15 V).

This ROM-less version addresses 2048 x 8 bits on an external memory (EPROM).