From WikiChip

Difference between revisions of "amd/duron/dhd1200amt1b"

m (Bot: corrected mem) |

m (Bot: Automated text replacement (-\| electrical += Yes +)) |

||

| Line 47: | Line 47: | ||

| max memory = 4 GiB | | max memory = 4 GiB | ||

| − | + | ||

| power = | | power = | ||

| v core = 1.75 V | | v core = 1.75 V | ||

Revision as of 21:56, 23 June 2017

Template:mpu The Duron 1200 based on the Morgan core was a 32-bit x86 microprocessor developed by AMD and introduced in late 2001. This model was part of the second generation of the Duron family. Designed based on AMD's K7 (a Thunderbird-derivative) on a 180 nm process, this MPU operated at 1200 MHz with a bus capable of 200 MT/s with a max TDP of 54.7 W and a typical TDP of 50.3 W.

Cache

- Main article: K7 § Cache

| Cache Info [Edit Values] | ||

| L1I$ | 64 KiB 65,536 B 0.0625 MiB |

1x64 KiB 2-way set associative |

| L1D$ | 64 KiB 65,536 B 0.0625 MiB |

1x64 KiB 2-way set associative |

| L2$ | 64 KiB 0.0625 MiB 65,536 B 6.103516e-5 GiB |

1x64 KiB 16-way set associative |

Graphics

This SoC has no integrated graphics processing unit.

Features

- Halt State

- Sleep State

Documents

DataSheet

- AMD Duron Processor Model 7 Data Sheet; Publication # 24310; Rev: G; Issue Date: January 2002.

Other

- AMD Duron Processor Model 7 Revision Guide; Publication # 24806; Rev: E; Issue Date: October 2003.

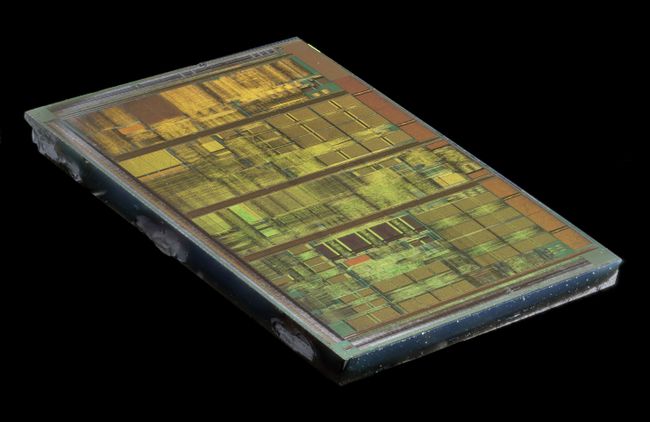

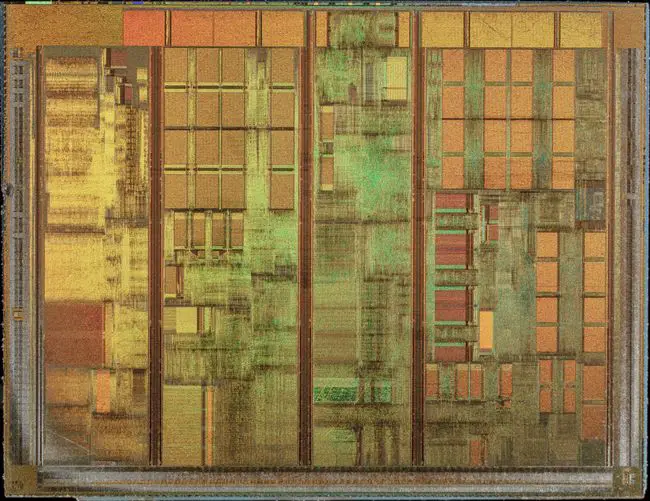

Die Shot

See also

Facts about "Duron 1200 (Morgan) - AMD"

| has feature | Halt State + and Sleep State + |

| l1d$ description | 2-way set associative + |

| l1d$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l1i$ description | 2-way set associative + |

| l1i$ size | 64 KiB (65,536 B, 0.0625 MiB) + |

| l2$ description | 16-way set associative + |

| l2$ size | 0.0625 MiB (64 KiB, 65,536 B, 6.103516e-5 GiB) + |