From WikiChip

Difference between revisions of "cavium/octeon/cn3110-300bg868-exp"

| Line 79: | Line 79: | ||

| packaging = Yes | | packaging = Yes | ||

| − | | package 0 = | + | | package 0 = HSBGA-868 |

| − | | package 0 type = | + | | package 0 type = HSBGA |

| package 0 pins = 868 | | package 0 pins = 868 | ||

| package 0 pitch = | | package 0 pitch = | ||

| Line 86: | Line 86: | ||

| package 0 length = | | package 0 length = | ||

| package 0 height = | | package 0 height = | ||

| − | | socket 0 = | + | | socket 0 = BGA-868 |

| − | | socket 0 type = | + | | socket 0 type = BGA |

}} | }} | ||

The '''CN3110-300 EXP''' is a {{arch|64}} [[single-core]] [[MIPS]] communication [[microprocessor]] designed by [[Cavium]] and introduced in [[2006]]. This processor, which incorporates a {{cavium|cnMIPS|l=arch}} core, operates at 300 MHz and dissipates 3 Watts. This processor includes a number of hardware accelerators for network processing such as [[compression]] & decompression, [[RegEx]] engine, [[TCP]], and [[QoS]]. This MPU supports up to 4 GiB of 64-bit DDR2-667 ECC memory. | The '''CN3110-300 EXP''' is a {{arch|64}} [[single-core]] [[MIPS]] communication [[microprocessor]] designed by [[Cavium]] and introduced in [[2006]]. This processor, which incorporates a {{cavium|cnMIPS|l=arch}} core, operates at 300 MHz and dissipates 3 Watts. This processor includes a number of hardware accelerators for network processing such as [[compression]] & decompression, [[RegEx]] engine, [[TCP]], and [[QoS]]. This MPU supports up to 4 GiB of 64-bit DDR2-667 ECC memory. | ||

Revision as of 18:23, 9 December 2016

Template:mpu The CN3110-300 EXP is a 64-bit single-core MIPS communication microprocessor designed by Cavium and introduced in 2006. This processor, which incorporates a cnMIPS core, operates at 300 MHz and dissipates 3 Watts. This processor includes a number of hardware accelerators for network processing such as compression & decompression, RegEx engine, TCP, and QoS. This MPU supports up to 4 GiB of 64-bit DDR2-667 ECC memory.

Contents

Cache

- Main article: cnMIPS § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Optional low-latency controller for content-based processing and meta data

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Expansions

|

Expansion Options

|

||||||||||||||||||||||||

|

||||||||||||||||||||||||

Networking

|

Networking

|

||||||||

|

||||||||

Features

Hardware acceleration units:

- Regular Expression

- Compression/Decompression (e.g. GZIP)

- QoS

- TCP Acceleration

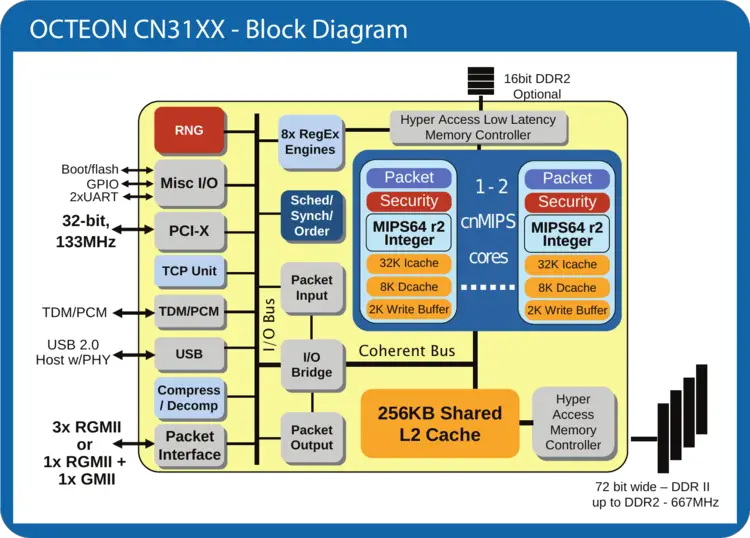

Block diagram

Datasheet

Facts about "CN3110-300 EXP - Cavium"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | CN3110-300 EXP - Cavium#package + |

| base frequency | 300 MHz (0.3 GHz, 300,000 kHz) + |

| core count | 1 + |

| core name | cnMIPS + |

| designer | Cavium + |

| family | OCTEON + |

| first announced | January 30, 2006 + |

| first launched | May 1, 2006 + |

| full page name | cavium/octeon/cn3110-300bg868-exp + |

| has ecc memory support | true + |

| has hardware accelerators for data compression | true + |

| has hardware accelerators for data decompression | true + |

| has hardware accelerators for network quality of service processing | true + |

| has hardware accelerators for regular expression | true + |

| has hardware accelerators for tcp packet processing | true + |

| instance of | microprocessor + |

| isa | MIPS64 + |

| isa family | MIPS + |

| l1$ size | 40 KiB (40,960 B, 0.0391 MiB) + |

| l1d$ description | 64-way set associative + |

| l1d$ size | 8 KiB (8,192 B, 0.00781 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 32 KiB (32,768 B, 0.0313 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 0.25 MiB (256 KiB, 262,144 B, 2.441406e-4 GiB) + |

| ldate | May 1, 2006 + |

| main image |  + + |

| manufacturer | TSMC + |

| market segment | Embedded + |

| max cpu count | 1 + |

| max memory | 4,096 MiB (4,194,304 KiB, 4,294,967,296 B, 4 GiB, 0.00391 TiB) + |

| max memory bandwidth | 4.97 GiB/s (5,089.28 MiB/s, 5.336 GB/s, 5,336.497 MB/s, 0.00485 TiB/s, 0.00534 TB/s) + and 1.24 GiB/s (1,269.76 MiB/s, 1.331 GB/s, 1,331.44 MB/s, 0.00121 TiB/s, 0.00133 TB/s) + |

| max memory channels | 1 + |

| microarchitecture | cnMIPS + |

| model number | CN3110-300 EXP + |

| name | Cavium CN3110-300 EXP + |

| package | HSBGA-868 + |

| part number | CN3110-300BG868-EXP + |

| power dissipation | 3 W (3,000 mW, 0.00402 hp, 0.003 kW) + |

| process | 130 nm (0.13 μm, 1.3e-4 mm) + |

| release price | $ 49.00 (€ 44.10, £ 39.69, ¥ 5,063.17) + |

| series | CN3100 + |

| smp max ways | 1 + |

| supported memory type | DDR2-667 + |

| technology | CMOS + |

| thread count | 1 + |

| word size | 64 bit (8 octets, 16 nibbles) + |