| Line 12: | Line 12: | ||

| market = Industrial | | market = Industrial | ||

| first announced = 2013 | | first announced = 2013 | ||

| − | | first launched = 2014 | + | | first launched = September, 2014 |

| last order = | | last order = | ||

| last shipment = | | last shipment = | ||

| Line 35: | Line 35: | ||

| transistors = | | transistors = | ||

| technology = CMOS | | technology = CMOS | ||

| − | | die area = | + | | die area = 411.6 mm² |

| die width = 21.1 mm | | die width = 21.1 mm | ||

| die length = 19.5 mm | | die length = 19.5 mm | ||

| Line 77: | Line 77: | ||

| socket 0 type = BGA | | socket 0 type = BGA | ||

}} | }} | ||

| − | '''PEZY-SC''' ('''PEZY Super Computer''') is second generation [[many-core microprocessor]] developed by [[PEZY]] in 2014. PEZY-SC contains 2 {{armh|ARM926}} cores ({{arm|ARMv5TEJ}}) along with 1024 simpler RISC cores. Operating at 733 MHz, the processor is said to have peach performance of 3.0 TFLOPS (single-precision) and 1.5 TFLOPS (double-precision). PEZY-SC was designed using 580 million gates and manufactured on TSMC's [[28 nm process]]. The PEZY-SC is used in a number of [[TOP500]] & [[Green500]] supercomputers as the world's most efficient supercomputers. | + | '''PEZY-SC''' ('''PEZY Super Computer''') is second generation [[many-core microprocessor]] developed by [[PEZY]] in 2014. PEZY-SC contains 2 {{armh|ARM926}} cores ({{arm|ARMv5TEJ}}) along with 1024 simpler RISC cores. Operating at 733 MHz, the processor is said to have peach performance of 3.0 TFLOPS (single-precision) and 1.5 TFLOPS (double-precision). PEZY-SC was designed using 580 million gates and manufactured on TSMC's 28HPC+ ([[28 nm process]]). The PEZY-SC is used in a number of [[TOP500]] & [[Green500]] supercomputers as the world's most efficient supercomputers. |

== Overview == | == Overview == | ||

| Line 84: | Line 84: | ||

In June of 2015, PEZY-SC-based [[supercomputer]]s took all top 3 spots on the [[Green500]] listing as the 3 most efficient supercomputers. PEZY-SC powers [[Shoubu]] (1,181,952 cores, ? kW, 605.624 TFlop/s [[Linpack]] Rmax), and [[Suiren Blue]] (262,656 cores, 40.86 kW, 247.752 TFlop/s Linpack Rmax), and [[Suiren]] (328,480 cores, 48.90 kW, 271.782 TFlop/s Linpack Rmax) supercomputers (ranked 1, 2, and 3 respectively). | In June of 2015, PEZY-SC-based [[supercomputer]]s took all top 3 spots on the [[Green500]] listing as the 3 most efficient supercomputers. PEZY-SC powers [[Shoubu]] (1,181,952 cores, ? kW, 605.624 TFlop/s [[Linpack]] Rmax), and [[Suiren Blue]] (262,656 cores, 40.86 kW, 247.752 TFlop/s Linpack Rmax), and [[Suiren]] (328,480 cores, 48.90 kW, 271.782 TFlop/s Linpack Rmax) supercomputers (ranked 1, 2, and 3 respectively). | ||

| + | |||

| + | == Architecture == | ||

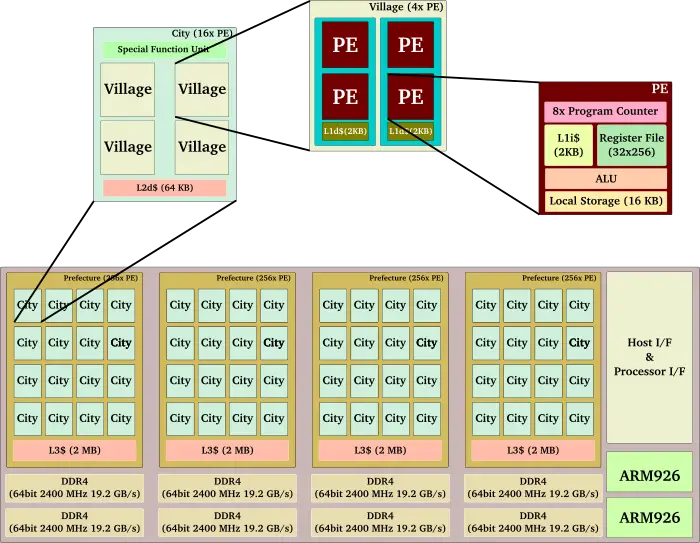

| + | The PEZY-SC microprocessors is made of 4 blocks called "Prefectures". The Prefecture contains 2 MB of L3$ enclosed by 16 smaller blocks called "Cities". Each City is made of 64 KB of L2$, a number of special function units, and 4 smaller blocks called "Villages". A village is a block of 4 execution units. For ever 2 execution units there are 2 KB of L1d$. | ||

| + | |||

| + | [[File:pezy-sc arch.svg|700px]] | ||

| + | |||

| + | === Processor Element (PE) === | ||

| + | The PE are the individual execution cores. | ||

| + | {{expand section}} | ||

== Cache == | == Cache == | ||

| Line 126: | Line 135: | ||

| sata ports = | | sata ports = | ||

| integrated lan = | | integrated lan = | ||

| − | | uart = | + | | uart = Yes |

| − | | gp io = | + | | gp io = Yes |

}} | }} | ||

| Line 135: | Line 144: | ||

* [https://www.top500.org/system/178540 Suiren Blue on TOP500] | * [https://www.top500.org/system/178540 Suiren Blue on TOP500] | ||

* [http://pc.watch.impress.co.jp/docs/news/714768.html Japanese supercomputer "PEZY system" has monopolized the 1 to 3-position of the Green500] | * [http://pc.watch.impress.co.jp/docs/news/714768.html Japanese supercomputer "PEZY system" has monopolized the 1 to 3-position of the Green500] | ||

| + | * [https://www.youtube.com/watch?v=_9Z1q0Kn2Qs 省エネ 液浸冷却小型スーパーコンピュータ ZettaScaler1.5] | ||

Revision as of 17:58, 6 September 2016

Template:mpu PEZY-SC (PEZY Super Computer) is second generation many-core microprocessor developed by PEZY in 2014. PEZY-SC contains 2 ARM926 cores (ARMv5TEJ) along with 1024 simpler RISC cores. Operating at 733 MHz, the processor is said to have peach performance of 3.0 TFLOPS (single-precision) and 1.5 TFLOPS (double-precision). PEZY-SC was designed using 580 million gates and manufactured on TSMC's 28HPC+ (28 nm process). The PEZY-SC is used in a number of TOP500 & Green500 supercomputers as the world's most efficient supercomputers.

Contents

Overview

- See also: PEZY-1

The PEZY-SC (SC for "Super Computer") is PEZY's second generation microprocessors which builds upon the PEZY-1. The chip contains exactly twice as many cores and incorporates a large amount of cache including 8 MB of L3$.

In June of 2015, PEZY-SC-based supercomputers took all top 3 spots on the Green500 listing as the 3 most efficient supercomputers. PEZY-SC powers Shoubu (1,181,952 cores, ? kW, 605.624 TFlop/s Linpack Rmax), and Suiren Blue (262,656 cores, 40.86 kW, 247.752 TFlop/s Linpack Rmax), and Suiren (328,480 cores, 48.90 kW, 271.782 TFlop/s Linpack Rmax) supercomputers (ranked 1, 2, and 3 respectively).

Architecture

The PEZY-SC microprocessors is made of 4 blocks called "Prefectures". The Prefecture contains 2 MB of L3$ enclosed by 16 smaller blocks called "Cities". Each City is made of 64 KB of L2$, a number of special function units, and 4 smaller blocks called "Villages". A village is a block of 4 execution units. For ever 2 execution units there are 2 KB of L1d$.

Processor Element (PE)

The PE are the individual execution cores.

| This section requires expansion; you can help adding the missing info. |

Cache

PEZY-SC's cache is separate from the ARM926's cache which has an L1$ of 32KB (2x) and 64KB L2$ (shared).

| Cache Info [Edit Values] | ||

| L1$ | 1 MB "MB" is not declared as a valid unit of measurement for this property. |

|

| L2$ | 4 MB "MB" is not declared as a valid unit of measurement for this property. |

|

| L3$ | 8 MB "MB" is not declared as a valid unit of measurement for this property. |

|

Memory controller

| Integrated Memory Controller | |

| Type | DDR4-2400 |

| Controllers | 1 |

| Channels | 8 |

| Bandwidth (single) | 19,200 MB/s |

| Bandwidth (dual) | 38,400 MB/s |

| Bandwidth (quad) | 76,800 MB/s |

| Bandwidth (octa) | 153,600 MB/s |