From WikiChip

Difference between revisions of "ambric/am2000/am2045b"

| Line 103: | Line 103: | ||

* 128x [[has feature::GPIO]] @ 100 MHz | * 128x [[has feature::GPIO]] @ 100 MHz | ||

* [[has feature::serial flash]] | * [[has feature::serial flash]] | ||

| + | |||

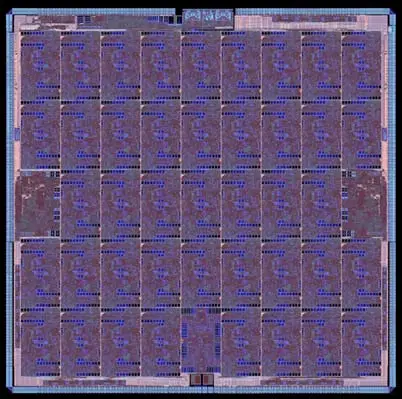

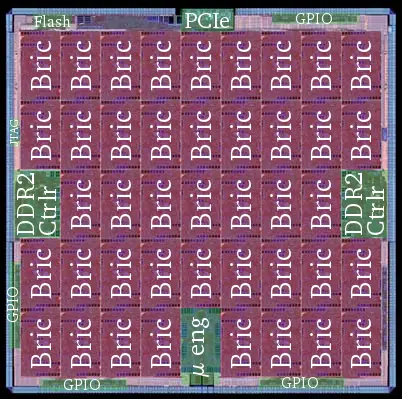

| + | == Die Shot == | ||

| + | {| | ||

| + | | [[File:Am2045 die shot.png]] || [[File:Am2045 die shot (annotated).png]] | ||

| + | |} | ||

Revision as of 03:34, 25 June 2016

Template:mpu Am2045B was Ambric's flagship MPPA introduced in late 2007. This model was made of 42 Brics arranged as a grid, making up a total of 336 32-bit RICS-like cores operating asynchronously at 1-350 MHz. This was an enhanced version of the original which featured a higher bandwidth network on a chip (Ambric claimed up to 40 percent improvement), operated at higher frequency, and provided up to 1.2 trillion operations per seconds theoretical peak computation. This model also had lower power consumption over the original.

Architecture

- Main article: Am2000 § Architecture

The Am2045B is made of 42 homogeneous 'Brics' laid out in a grid to form 336 cores.

General layout:

- 42x Brics

Memory controller

| Integrated Memory Controller | |

| Type | DDR2-400 |

| Controllers | 2 |

| Channels | 1 |

| Max memory | 4 GB |

Expansions

- PCIe

- JTAG

- 128x GPIO @ 100 MHz

- serial flash

Die Shot

|

|