From WikiChip

Difference between revisions of "amd/am486/am486dx4-100nv8t"

| Line 3: | Line 3: | ||

| name = Am486DX4-100NV8T | | name = Am486DX4-100NV8T | ||

| no image = | | no image = | ||

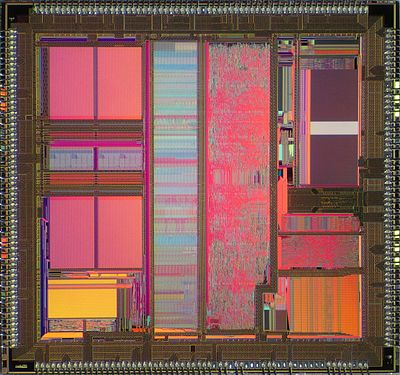

| − | | image = AMD | + | | image = Ic-photo-AMD--A80486DX4-100NV8T-(486-CPU).png |

| image size = | | image size = | ||

| caption = A80486DX4-100NV8T | | caption = A80486DX4-100NV8T | ||

| Line 97: | Line 97: | ||

<gallery> | <gallery> | ||

File:Amd-am486dx4-100-wt.jpg| | File:Amd-am486dx4-100-wt.jpg| | ||

| + | File:AMD Am486 DX4 100 NV8T CPU.jpg| | ||

</gallery> | </gallery> | ||

Revision as of 03:15, 17 May 2016

Template:mpu Am486DX2-100NV8T was an 80486-compatible microprocessor introduced by AMD in 1995 following the conclusion of the legal battle with Intel. This processor had a clock multiplier of 3 having base frequency of 100 MHz with a bus frequency of 33 MHz. This model is is a modified version of Am486DX4-100V8T (and earlier Am486DX4-100) that no longer included Intel's ICE microcode.

Cache

- Main article: 80486 § Cache

| Cache Info [Edit Values] | ||

| L1$ | 8 KB "KB" is not declared as a valid unit of measurement for this property. |

1x8 KB 4-way set associative (unified, write-through policy) |

Graphics

This chip had no integrated graphics processing unit.