From WikiChip

File list

This special page shows all uploaded files.

First page |

Previous page |

Next page |

Last page |

| Date | Name | Thumbnail | Size | User | Description | Versions |

|---|---|---|---|---|---|---|

| 16:06, 29 December 2019 | qualcomm-snapdragon-865-5g-mobile-platform-chip-back.jpg (file) |  |

2.03 MB | David | Snapdragon 865 back. Photo by Qualcomm. | 1 |

| 16:06, 29 December 2019 | qualcomm-snapdragon-865-5g-mobile-platform-chip-front.jpg (file) |  |

2.65 MB | David | Snapdragon 865 front. Photo by Qualcomm. | 1 |

| 17:41, 29 December 2019 | qualcomm-snapdragon-865-5g-mobile-platform-product-brief.pdf (file) |  |

347 KB | David | Snapdragon 865 PB | 1 |

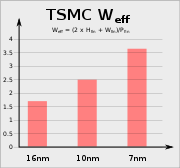

| 01:50, 30 December 2019 | tsmc-weff-16-10-7.svg (file) |  |

22 KB | David | WikiChip plot of TSMC Weff N16, N10, and N7. | 1 |

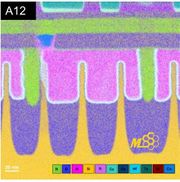

| 02:25, 30 December 2019 | mss-n7-a12.jpg (file) |  |

95 KB | David | TSMC N7 elements of Apple's A12 SoC. Image by MSS Corps. | 1 |

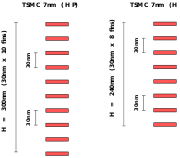

| 02:39, 30 December 2019 | n7 cell height.svg (file) |  |

22 KB | David | WikiChip drawing of TSMC N7 cell height. | 1 |

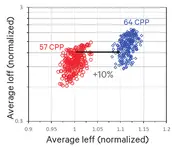

| 02:52, 30 December 2019 | sdm855-n7-hd-hp-ieff.png (file) |  |

56 KB | David | Snapdragon 855 difference in Ieff HD vs HP 7nm cells. Graph by Qualcomm. | 1 |

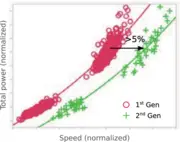

| 03:37, 30 December 2019 | vlsi-2019-n7p-2nd-gen-perf.png (file) |  |

175 KB | David | TSMC N7P perf difference. | 1 |

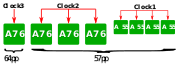

| 04:13, 30 December 2019 | sdm855-clocks.svg (file) |  |

22 KB | David | Snapdragon 855 clocks. Diagram by WikiChip. | 1 |

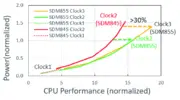

| 04:16, 30 December 2019 | 855 clock improvement.png (file) |  |

42 KB | David | Snapdragon 855 clock improvements | 1 |

| 06:21, 30 December 2019 | 7nm densities.svg (file) |  |

79 KB | David | 2 | |

| 07:25, 30 December 2019 | n7 overview slide.jpg (file) |  |

1.47 MB | David | TSMC N7 overview slide. Photo by WikiChip. | 1 |

| 17:36, 30 December 2019 | AMD Zen 2 CCD.jpg (file) |  |

88.11 MB | QuietRub | Polysilicon layer of a Core Complex Die of an AMD EPYC 7702 ES. Die size 10.32 mm × 7.34 mm, resolution 22160 dpi. Author: Fritzchens Fritz https://www.flickr.com/photos/130561288@N04/49045449908/ | 1 |

| 16:32, 2 January 2020 | dimensity1000.png (file) |  |

298 KB | David | MediaTek Dimensity 1000 | 1 |

| 17:30, 2 January 2020 | MediaTek-Dimensity-1000-inf.pdf (file) |  |

5.18 MB | David | MediaTek [[Dimensity 1000] infographic. | 1 |

| 17:39, 2 January 2020 | mediatek dimensity 1000 2.jpg (file) |  |

727 KB | David | MediaTek Dimensity 1000 infographic. | 1 |

| 00:38, 13 January 2020 | vanilla-5 core.png (file) |  |

308 KB | David | Vanilla-5 core. | 1 |

| 00:39, 13 January 2020 | vanilla-5 routing.png (file) |  |

316 KB | David | Vanilla-5 routing. | 1 |

| 00:55, 13 January 2020 | vanilla-5 (annotated).png (file) |  |

135 KB | David | Vanilla-5 core annotated. | 1 |

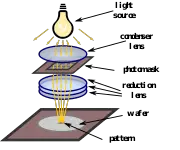

| 01:16, 22 January 2020 | mask diagram.svg (file) |  |

45 KB | David | photomask diagram by WikiChip. | 1 |

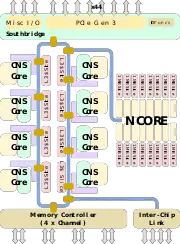

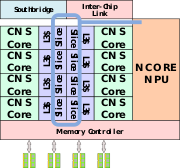

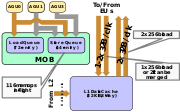

| 18:03, 22 January 2020 | cha soc block diagram.svg (file) |  |

78 KB | David | WikiChip diagram of the {{centaur|CHA|l=arch}} SoC | 1 |

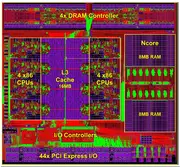

| 18:13, 22 January 2020 | cha soc.png (file) |  |

3.62 MB | David | Centaur {{centaur|CHA|l=arch}} SoC. | 1 |

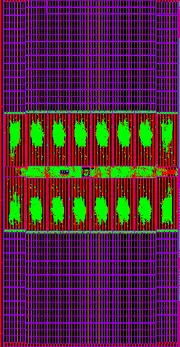

| 18:13, 22 January 2020 | cha core group.png (file) |  |

1.4 MB | David | Centaur {{centaur|CHA|l=arch}} core group. | 1 |

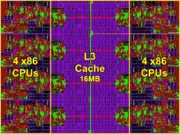

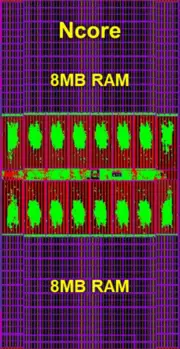

| 18:13, 22 January 2020 | cha soc ncore.png (file) |  |

701 KB | David | Centaur {{centaur|CHA|l=arch}} ncore. | 1 |

| 18:17, 22 January 2020 | cha soc ncore (2).png (file) |  |

6 KB | David | Centaur {{centtech|CHA|l=arch}} ncore. | 1 |

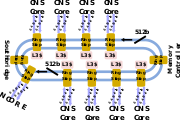

| 14:31, 23 January 2020 | cns block diagram.svg (file) |  |

119 KB | David | 2 | |

| 21:37, 23 January 2020 | ncore slices.svg (file) |  |

96 KB | David | Centaur {{centtech|CHA|l=arch}} diagram of the NCORE by WikiChip. | 1 |

| 22:25, 23 January 2020 | cha ring.svg (file) |  |

60 KB | David | Centaur {{centtech|CHA|l=arch}} ring interconnect diagram by WikiChip. | 1 |

| 23:35, 23 January 2020 | cha soc overview.svg (file) |  |

44 KB | David | Centaur {{centtech|CHA|l=arch}} SoC overview by WikiChip. | 1 |

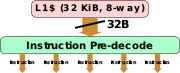

| 01:29, 24 January 2020 | cns icache.svg (file) |  |

12 KB | David | Centaur {{centtech|CHA|l=arch}} CNS instruction cache by diagram WikiChip. | 1 |

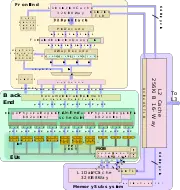

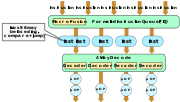

| 01:32, 24 January 2020 | cns decode.svg (file) |  |

33 KB | David | WikiChip diagram of Centaur's {{centtech|CHA|l=arch}} CNS decode. | 1 |

| 01:54, 24 January 2020 | cns mem subsys.svg (file) |  |

23 KB | David | WikiChip diagram of Centaur's {{centtech|CHA|l=arch}} CNS memory subsystem. | 1 |

| 03:30, 24 January 2020 | cha cns core die.png (file) |  |

103 KB | David | Centaur {{centtech|CHA|l=arch}} CNS core die. | 1 |

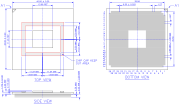

| 19:49, 27 January 2020 | OPGA-754.svg (file) |  |

1 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 754 Pin Package", AMD Publ. #31410 | 1 |

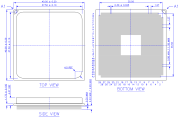

| 09:21, 29 January 2020 | OPGA-754 lidded diag.svg (file) |  |

38 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 754 Pin Package", AMD Publ. #31410 | 1 |

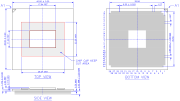

| 09:27, 29 January 2020 | OPGA-754 lidless B1 diag.svg (file) |  |

45 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 754 Pin Package", AMD Publ. #31410 | 1 |

| 09:33, 29 January 2020 | OPGA-754 lidless B2 diag.svg (file) |  |

49 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 754 Pin Package", AMD Publ. #31410 | 1 |

| 09:35, 29 January 2020 | OPGA-754 lidless B3 diag.svg (file) |  |

50 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 754 Pin Package", AMD Publ. #31410 | 1 |

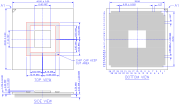

| 09:37, 29 January 2020 | Socket 754 diag.svg (file) |  |

22 KB | QuietRub | Own work based on "Socket 754 Design and Qualification Requirements", AMD Publ. #24850 | 1 |

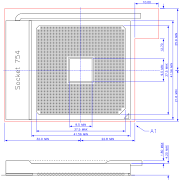

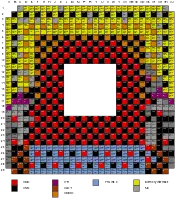

| 09:40, 29 January 2020 | OPGA-754 lidded pinmap.svg (file) |  |

148 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 754 Pin Package", AMD Publ. #31410 | 1 |

| 13:43, 30 January 2020 | CPGA-940.svg (file) |  |

1 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 940 Pin Package", AMD Publ. #31412 | 1 |

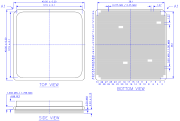

| 14:43, 30 January 2020 | CPGA-940 diag.svg (file) |  |

37 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 940 Pin Package", AMD Publ. #31412 | 1 |

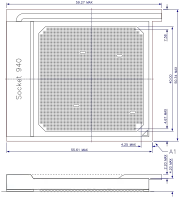

| 14:45, 30 January 2020 | Socket 940 diag.svg (file) |  |

18 KB | QuietRub | Own work based on "AMD Socket 940 Design Specification", AMD Publ. # 25766 | 1 |

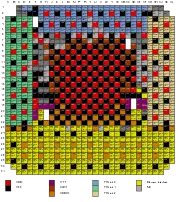

| 14:47, 30 January 2020 | CPGA-940 pinmap.svg (file) |  |

197 KB | QuietRub | Own work based on "AMD Functional Data Sheet, 940 Pin Package", AMD Publ. #31412 | 1 |

| 15:02, 30 January 2020 | K8 Opteron MP topology.svg (file) | 64 KB | QuietRub | Typo. | 2 | |

| 02:28, 1 February 2020 | 16433-1 NNP-announce NNP-T brief v4.3.pdf (file) |  |

695 KB | David | Intel Nervana {{nervana|NNP}}-T PB. | 1 |

| 03:16, 1 February 2020 | 16433-1 NNP-announce NNP-I brief v5.1.pdf (file) |  |

414 KB | David | Nervan {{nervana|NNP}}-I PB. | 1 |

| 03:51, 1 February 2020 | nnp-i ruler.jpg (file) |  |

1.81 MB | David | Nervana {{nervana|NNP}}-I ruler. | 1 |

| 03:52, 1 February 2020 | supermicro nnp-i chassis.jpg (file) |  |

2.32 MB | David | Nervana {{nervana|NNP}}-I chassis by Supermicro. | 1 |

| 11:37, 1 February 2020 | ai hw summit supermicro ref pod.jpeg (file) |  |

3.18 MB | David | Nervana {{nervana|NNP}}-T reference pod. | 1 |

First page |

Previous page |

Next page |

Last page |