From WikiChip

Core i7-6950X Extreme Edition - Intel

Template:mpu The Core i7-6950X Extreme Edition is a 64-bit deca-core top-of-the-line MPU introduced by Intel for the enthusiasts market in mid-2016. The i7-6950X replaced the i7-5960X as Intel's flagship microprocessor based on Broadwell microarchitecture - also becoming the first consumer-class deca-core microprocessor.

Contents

Cache

- Main article: Broadwell § Cache

| Cache Info [Edit Values] | ||

| L1I$ | 320 KiB 327,680 B 0.313 MiB |

10x32 KiB 8-way set associative (per core) |

| L1D$ | 320 KiB 327,680 B 0.313 MiB |

10x32 KiB 8-way set associative (per core) |

| L2$ | 2.5 MiB 2,560 KiB 2,621,440 B 0.00244 GiB |

10x256 KiB 8-way set associative (per core) |

| L3$ | 25 MiB 25,600 KiB 26,214,400 B 0.0244 GiB |

10x2.5 MiB 20-way set associative (shared) |

Graphics

This processor has no integrated graphics processing unit.

Memory controller

| Integrated Memory Controller | |

| Type | DDR4-2133, DDR4-2400 |

| Controllers | 1 |

| Channels | 4 |

| ECC Support | No |

| Max bandwidth | 76.8 GB/s |

| Bandwidth (single) | 19,200 MB/s |

| Bandwidth (dual) | 38,400 MB/s |

| Bandwidth (quad) | 76,800 MB/s |

| Max memory | 128 GiB |

Expansions

|

Expansion Options

|

||||||||

|

||||||||

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||

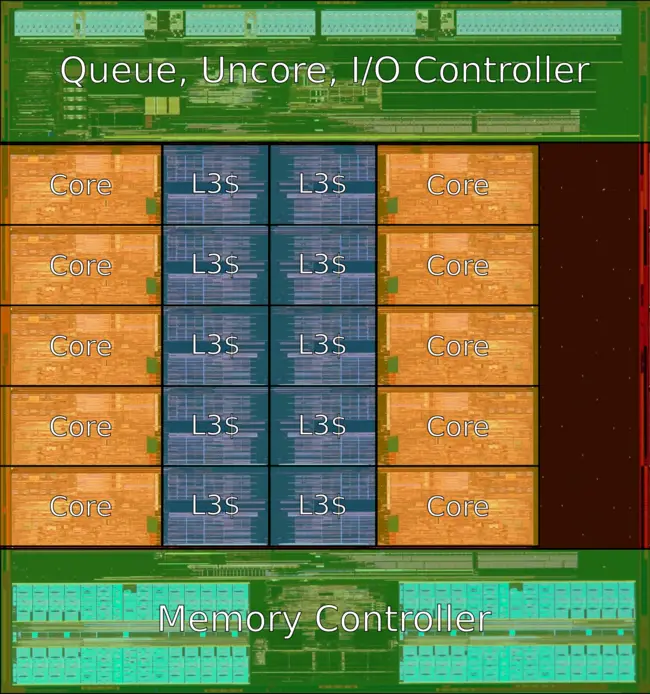

Die Shot

- 3,400,000,000 transistors

- 246 mm2

Documents

See also

Facts about "Core i7-6950X Extreme Edition - Intel"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Core i7-6950X Extreme Edition - Intel#io + |

| has advanced vector extensions | true + |

| has advanced vector extensions 2 | true + |

| has extended page tables support | true + |

| has feature | Advanced Vector Extensions +, Advanced Vector Extensions 2 +, Advanced Encryption Standard Instruction Set Extension +, Hyper-Threading Technology +, Turbo Boost Technology 2.0 +, Turbo Boost Max Technology 3.0 +, Enhanced SpeedStep Technology + and Extended Page Tables + |

| has intel enhanced speedstep technology | true + |

| has intel turbo boost max technology 3 0 | true + |

| has intel turbo boost technology 2 0 | true + |

| has second level address translation support | true + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 320 KiB (327,680 B, 0.313 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 320 KiB (327,680 B, 0.313 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 2.5 MiB (2,560 KiB, 2,621,440 B, 0.00244 GiB) + |

| l3$ description | 20-way set associative + |

| l3$ size | 25 MiB (25,600 KiB, 26,214,400 B, 0.0244 GiB) + |

| max pcie lanes | 40 + |