m (Bot: Automated text replacement (-|avx512=No +)) |

|||

| Line 166: | Line 166: | ||

|avx=Yes | |avx=Yes | ||

|avx2=Yes | |avx2=Yes | ||

| − | + | ||

|abm=Yes | |abm=Yes | ||

|tbm=No | |tbm=No | ||

Revision as of 00:20, 11 July 2017

Template:mpu Ryzen 7 1800X is a 64-bit octa-core high-end performance x86 desktop SoC introduced by AMD in early 2017. The 1800X is AMD's flagship model based on their Zen microarchitecture, fabricated on a 14 nm process. The 1800X operates at a base frequency of 3.6 GHz with a TDP of 95 W and a Boost frequency of 4.0 GHz. This MPU supports up to 64 GiB of dual-channel DDR4-3200 ECC memory.

Contents

Overview

- Main article: Zen

The Ryzen 7 1800X is AMD's flagship system on chip based on the Zen microarchitecture. The 1800X integrates eight x86 cores and is the first AMD processor to support 2-way simultaneous multithreading. Sporting a base frequency of 3.6 GHz and a Boost frequency of 4.0 GHz, the 1800X is the fastest of the Ryzen processors. The 1800X is a complete SoC integrating a DDR4 memory controller, along with the entire southbridge on-die. The 1800X includes 16 PCIe lanes for a GPU along with 4 more lanes for storage (NVMe or 2 ports SATA Express).

Cache

- Main article: Zen § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller

This processor incorporates 2 DDR4 PHYs, each supporting 1 channel of 64-bit data plus ECC with 2 DIMMs per channel. DIMMs of rates 1,333 MT/s - 3,200 MT/s are supported (UDIMM/SODIMM). Note that despite AMD's support for memory rates of 3,200 MT/s and possibly higher, rates beyond 2666 MT/s exceeds the JEDEC specification and is thus considered overclocking which voids AMD product warranty and likely any vendor or retailer warranties as well.

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

| [Edit] Memory Configurations | |||

|---|---|---|---|

| Dual Channel | Single Rank | 2 DIMMs | DDR4-2666 |

| 4 DIMMs | DDR4-2133 | ||

| Double Rank | 2 DIMMs | DDR4-2400 | |

| 4 DIMMs | DDR4-1866 | ||

Expansions

The Ryzen 7 1800X includes 20 PCIe lanes supporting Gen1, Gen2, and Gen3: 16 for a DGP and 4 for storage (NVMe or 2 ports SATA Express). PHY of 16 lanes may each have a maximum of 8 PCIe ports (x1, x2, x4, x8, x16).

|

Expansion Options

|

||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||

- eMMC, LPC, SMBus, SPI/eSPI

Audio

Support Azalia High Definition Audio

Graphics

This processor has no integrated graphics.

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

- This model has full XFR support, allowing for an additional +100 MHz boost frequency.

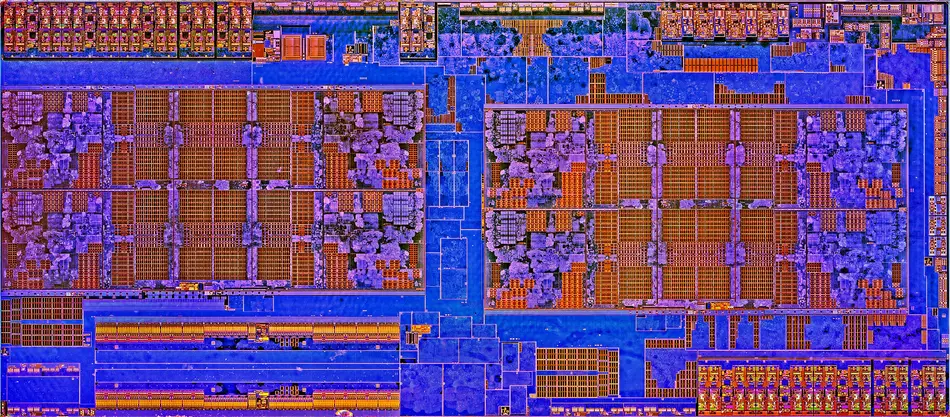

Die Shot

- See also: Zen § Die Shot

- 14 nm process

- 12 metal layers

- 2,000 meters of signals

- 4,800,000,000 transistors

- 22.01 mm x 8.87 mm

- ~195.228 mm²

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Ryzen 7 1800X - AMD#io + |

| has advanced vector extensions | true + |

| has advanced vector extensions 2 | true + |

| has amd amd-v technology | true + |

| has amd amd-vi technology | true + |

| has amd extended frequency range | true + |

| has amd sensemi technology | true + |

| has ecc memory support | true + |

| has feature | Advanced Vector Extensions +, Advanced Vector Extensions 2 +, Advanced Encryption Standard Instruction Set Extension +, SenseMI Technology + and Extended Frequency Range + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| l1$ size | 768 KiB (786,432 B, 0.75 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 256 KiB (262,144 B, 0.25 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 512 KiB (524,288 B, 0.5 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 4 MiB (4,096 KiB, 4,194,304 B, 0.00391 GiB) + |

| l3$ description | 16-way set associative + |

| l3$ size | 16 MiB (16,384 KiB, 16,777,216 B, 0.0156 GiB) + |

| max memory bandwidth | 39.74 GiB/s (40,693.76 MiB/s, 42.671 GB/s, 42,670.5 MB/s, 0.0388 TiB/s, 0.0427 TB/s) + |

| max memory channels | 2 + |

| max pcie lanes | 20 + |

| supported memory type | DDR4-2666 + |