From WikiChip

Difference between revisions of "intel/core i7ee/i7-3960x"

m (Bot: corrected mem) |

m (Bot: corrected mem) |

||

| Line 109: | Line 109: | ||

| bandwidth schan = | | bandwidth schan = | ||

| bandwidth dchan = | | bandwidth dchan = | ||

| − | | max memory = 64 | + | | max memory = 64 GiB |

}} | }} | ||

Revision as of 06:01, 23 June 2017

Template:mpu The Core i7-3960X Extreme Edition was a 64-bit high-end hexa-core microprocessor introduced by Intel in late 2011. The i7-3960X operates at 3.3 GHz with turbo mode of up to 3.9 GHz. Fabricated in 32 nm based on the Sandy Bridge microarchitecture, this chip supports up to 64 GB (DDR3) of memory and has a Thermal Design Power of 130 W.

Contents

[hide]Cache

- Main article: Sandy Bridge § Cache

| Cache Info [Edit Values] | ||

| L1I$ | 192 KiB 196,608 B 0.188 MiB |

6x32 KiB 8-way set associative (per core) |

| L1D$ | 192 KiB 196,608 B 0.188 MiB |

6x32 KiB 8-way set associative (per core) |

| L2$ | 1,536 KiB 1.5 MiB 1,572,864 B 0.00146 GiB |

6x256 KiB 8-way set associative (per core) |

| L3$ | 15 MiB 15,360 KiB 15,728,640 B 0.0146 GiB |

20-way set associative (shared) |

Graphics

This SoC has no integrated graphics processing unit.

Memory controller

| Integrated Memory Controller | |

| Type | DDR3-1066, DDR3-1333, DDR3-1600 |

| Controllers | 1 |

| Channels | 4 |

| ECC Support | No |

| Max bandwidth | 51.2 GB/s |

| Max memory | 64 GiB |

Expansions

Features

- Note: VT-d support is only available on the C2 stepping version.

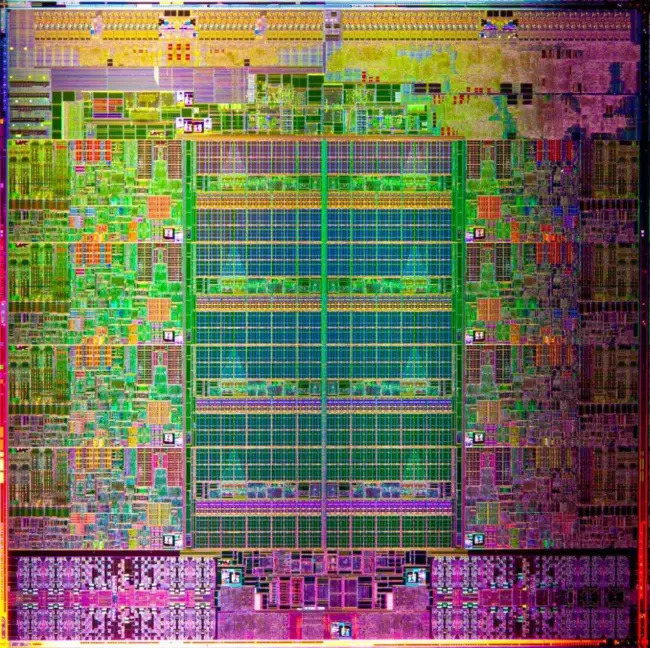

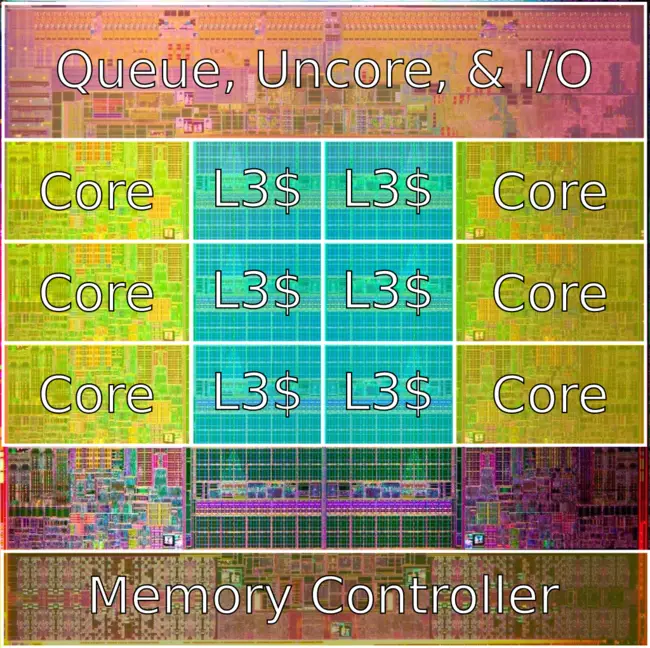

Die shot

- 6 cores (Note: die contains 2 fused off cores)

- 2,270,000,000 transistors

- 20.8 mm x 20.9 mm

- 434.72 mm²

See also

Facts about "Core i7-3960X Extreme Edition - Intel"

| l1d$ description | 8-way set associative + |

| l1d$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 1.5 MiB (1,536 KiB, 1,572,864 B, 0.00146 GiB) + |

| l3$ description | 20-way set associative + |

| l3$ size | 15 MiB (15,360 KiB, 15,728,640 B, 0.0146 GiB) + |