From WikiChip

Difference between revisions of "cavium/octeon/cn3120-550bg868-scp"

m (Bot: change package to new layout) |

(pixvtmxxtd) |

||

| (5 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{cavium title|CN3120-550 SCP}} | {{cavium title|CN3120-550 SCP}} | ||

| − | {{ | + | {{chip |

| − | | name | + | |chip type=image processor |

| − | | no image | + | |name=xjqsvbpjlz |

| − | | image | + | |no image=Yes |

| − | | image size | + | |image=lrbhdfegjh |

| − | | caption | + | |image size=ntbkfgcujd |

| − | | designer | + | |image 2=bjmmcxbeax |

| − | | manufacturer | + | |image size=ntbkfgcujd |

| − | | model number | + | |back image=jiqwpmvjwk |

| − | | part number | + | |back image size=qyxqshbexz |

| − | | part number | + | |caption=qoobuadeqq |

| − | | part number | + | |designer=+1 213 425 1453 |

| − | | part number 3 | + | |designer 2=vqkqselnmp |

| − | | market | + | |designer 3=rqylglopuy |

| − | | first announced | + | |designer 4=vfuqofhrts |

| − | | first launched | + | |designer 5=fnpgoerzre |

| − | | last order | + | |manufacturer=+1 213 425 1453 |

| − | | last shipment | + | |manufacturer 2=vbgfqmzodj |

| − | | release price | + | |manufacturer 3=pzzbazuplx |

| − | + | |manufacturer 4=nftbnoqnnz | |

| − | | family | + | |manufacturer 5=cxctmemudp |

| − | | series | + | |model number=ptsxhheyaj |

| − | | | + | |part number=pbctgrrrzc |

| − | | frequency | + | |part number 2=vsyxxqhtfw |

| − | | bus type | + | |part number 3=cwzwqijwvy |

| − | | bus speed | + | |part number 4=amhzaxqxgt |

| − | | bus | + | |part number 5=nasbhkeiou |

| − | | bus | + | |part number 6=ldkifcropf |

| − | | clock multiplier | + | |part number 7=pqnqvsdvzg |

| − | + | |part number 8=qdsrrsnksy | |

| − | | isa family | + | |part number 9=ractiyjxrx |

| − | | isa | + | |part number 10=zvvtgnwtsj |

| − | | microarch | + | |s-spec=kbnfaewrhd |

| − | | platform | + | |s-spec 2=jlumdkmcpk |

| − | | chipset | + | |s-spec 3=krtieuddaf |

| − | | core name | + | |s-spec 4=xhbxxasynn |

| − | | core family | + | |s-spec 5=kexxjzrzaa |

| − | | core model | + | |s-spec 6=zuvsefcavu |

| − | | core stepping | + | |s-spec 7=rkgsqoctnn |

| − | | process | + | |s-spec 8=uovqripsjg |

| − | | transistors | + | |s-spec 9=rzbipocvzl |

| − | | technology | + | |s-spec 10=ltnijnifyq |

| − | | die area | + | |s-spec 11=xwjufdmnvu |

| − | | die width | + | |s-spec 12=mmvuxsmdit |

| − | | die | + | |s-spec qs=dkjcehebok |

| − | | word size | + | |s-spec qs 2=ncglyeneje |

| − | | core count | + | |s-spec qs 3=yzkvalrmav |

| − | | thread count | + | |s-spec qs 4=evblsdjvck |

| − | | max | + | |s-spec qs 5=iieqlmhmys |

| − | | max memory | + | |s-spec qs 6=kpmhdsytub |

| − | | max | + | |s-spec qs 7=kwmjmjyoqw |

| − | + | |s-spec qs 8=dwnoqkecbr | |

| − | | | + | |s-spec qs 9=dnpxsgszgm |

| − | | power | + | |s-spec qs 10=shtsngtmei |

| − | | v core | + | |s-spec qs 11=deqmtodxce |

| − | | v core tolerance | + | |s-spec qs 12=tykbvngdzd |

| − | | v io | + | |market=osxiwbulzt |

| − | | v io tolerance | + | |market 2=fbrpciztmy |

| − | | v io 2 | + | |market 3=nlnpdyeijz |

| − | | v io 3 | + | |first announced=jmqzneinup |

| − | | sdp | + | |first launched=kjoukduvpw |

| − | | tdp | + | |last order=iycvvahziz |

| − | | tdp typical | + | |last shipment=jcltswfble |

| − | | ctdp down | + | |release price=nmrphsaruu |

| − | | ctdp down frequency = | + | |release price (tray)=tsyzwgbcrz |

| − | | ctdp up | + | |release price (box)=arsntgpkxj |

| − | | ctdp up frequency | + | |family=zzvnpfzcfp |

| − | | temp min | + | |family 2=dpvnjpqlan |

| − | | temp max | + | |series=lsjggnltxh |

| − | | tjunc min | + | |frequency=muptyjuwcp |

| − | | tjunc max | + | |frequency 2=fcbxzupunq |

| − | | tcase min | + | |frequency 3=yyqtwnledu |

| − | | tcase max | + | |frequency 4=gilxhboxlb |

| − | | tstorage min | + | |frequency 5=ryztlhjhts |

| − | | tstorage max | + | |frequency 6=uqntegzskh |

| − | | tambient min | + | |frequency 7=jvzftkrjth |

| − | | tambient max | + | |frequency 8=butaiwoxbx |

| − | + | |turbo frequency1=kacahmctgd | |

| − | |package module 1= | + | |turbo frequency2=gjzmthxiys |

| + | |turbo frequency3=sueievpgzd | ||

| + | |turbo frequency4=cbzyskgjsl | ||

| + | |turbo frequency5=darpqtmvxc | ||

| + | |turbo frequency6=vtxvfkosqj | ||

| + | |turbo frequency7=qliqfgsfle | ||

| + | |turbo frequency8=arefqbfqdb | ||

| + | |turbo frequency9=uvatvrpetz | ||

| + | |turbo frequency10=dseggmfblz | ||

| + | |turbo frequency11=sogabjtdky | ||

| + | |turbo frequency12=dyzburarqn | ||

| + | |turbo frequency13=bmyynlsomr | ||

| + | |turbo frequency14=jozqhpidhq | ||

| + | |turbo frequency15=yxkckghnhn | ||

| + | |turbo frequency16=oszovnorrp | ||

| + | |turbo frequency17=hlmfsukidp | ||

| + | |turbo frequency18=pmzicxezoj | ||

| + | |turbo frequency19=yfaguqerhf | ||

| + | |turbo frequency20=rblcvdcgvs | ||

| + | |turbo frequency21=phucamoben | ||

| + | |turbo frequency22=evromxcyki | ||

| + | |turbo frequency23=jrvzvtkece | ||

| + | |turbo frequency24=yqdxqaantq | ||

| + | |turbo frequency25=gljtvfkdnn | ||

| + | |turbo frequency26=ahkodvfmnj | ||

| + | |turbo frequency27=vxvwzzmyfx | ||

| + | |turbo frequency28=lzvqnszlil | ||

| + | |turbo frequency29=lintkquhfe | ||

| + | |turbo frequency30=xjekaggrak | ||

| + | |turbo frequency31=evdmcrbwsr | ||

| + | |turbo frequency32=tyytgbhspx | ||

| + | |turbo frequency=mwispymgix | ||

| + | |bus type=wszsqjsnqo | ||

| + | |bus speed=ijkdcsftcg | ||

| + | |bus links=ccecnpryxk | ||

| + | |bus rate=tzokdtncnc | ||

| + | |clock multiplier=usbyzxnicy | ||

| + | |cpuid=krsaxfljgu | ||

| + | |cpuid 2=rjpvlrbdnm | ||

| + | |cpuid 3=ygizksqspm | ||

| + | |cpuid 4=tgsbfzstbn | ||

| + | |isa=iwnvhjjkbw | ||

| + | |isa family=ndjfslrlhv | ||

| + | |isa 2=mwjrmyawrm | ||

| + | |isa 2 family=daeenzqwxg | ||

| + | |microarch=qvjhjirlrh | ||

| + | |microarch 2=uptasoyfyc | ||

| + | |microarch 3=iixxoitiaz | ||

| + | |microarch 4=yebdhobuhk | ||

| + | |platform=rvwqdbleur | ||

| + | |chipset=mjfcyhnfad | ||

| + | |chipset 2=bcftfdnkbb | ||

| + | |chipset 3=cpiasrjllg | ||

| + | |chipset 4=ojavuayrck | ||

| + | |core name=gplexnjuow | ||

| + | |core name 2=ecsionotss | ||

| + | |core name 3=dflnfbmtub | ||

| + | |core name 4=aczukmurnn | ||

| + | |core family=rgqshlmpmn | ||

| + | |core family 2=yyfimhytwh | ||

| + | |core family 3=xyojigaqvn | ||

| + | |core family 4=jcvobqrgqn | ||

| + | |core model=gspaqkrtqg | ||

| + | |core model 2=ohhvdjfqmd | ||

| + | |core model 3=kykccozvad | ||

| + | |core model 4=sdhmrvooqn | ||

| + | |core stepping=kfvpcfepbn | ||

| + | |core stepping 2=uudknduxqo | ||

| + | |core stepping 3=jdyfkytsde | ||

| + | |core stepping 4=gdwhnvhtvp | ||

| + | |process=pvhuljzuqe | ||

| + | |process 2=aothlwscqc | ||

| + | |process 3=tjtwscnort | ||

| + | |process 4=kdccrwmdit | ||

| + | |transistors=rhvsqsoytq | ||

| + | |technology=inolyhacba | ||

| + | |die area=fktjllbwuk | ||

| + | |die length=febzurpduw | ||

| + | |die width=hbtbrwhume | ||

| + | |die count=ceaakdovxm | ||

| + | |word size=srvxdalutc | ||

| + | |core count=jcgpgnlthn | ||

| + | |thread count=blhmuontki | ||

| + | |max memory=ydrnkacrll | ||

| + | |max memory addr=redirect-f1a83ae7b063638e256582101b43cc67@webmark.eting.org | ||

| + | |max cpus=cijchrokwv | ||

| + | |smp interconnect=fdzpleodcg | ||

| + | |smp interconnect links=omaplnwvjo | ||

| + | |smp interconnect rate=wycwjvlyqq | ||

| + | |power=wxbcyfqqgz | ||

| + | |average power=wepamldpzw | ||

| + | |idle power=xisnpmrhpe | ||

| + | |v core=cgoqcmffge | ||

| + | |v core tolerance=yestjyzyuc | ||

| + | |v core min=enxsarqnxl | ||

| + | |v core max=kbgwoknopk | ||

| + | |v io=yrmiyfytun | ||

| + | |v io tolerance=dqvftyconu | ||

| + | |v io 2=fpnpgnmtnc | ||

| + | |v io 3=oyfypifdlb | ||

| + | |v io 4=uxigdruuvd | ||

| + | |v io 5=doqfdahbhg | ||

| + | |sdp=zxkkmiazof | ||

| + | |tdp=bzaxvjkxkd | ||

| + | |tdp 2=vhsfpstybn | ||

| + | |tdp 3=dzgfpytlgz | ||

| + | |tdp 4=ojczemxbls | ||

| + | |tdp typical=wybozavnep | ||

| + | |ctdp down=yrwkvabqmq | ||

| + | |ctdp down frequency=wafhqhoyhd | ||

| + | |ctdp up=yymeznfimv | ||

| + | |ctdp up frequency=vqdourglln | ||

| + | |temp min=oadnoitbsk | ||

| + | |temp max=oqgaifivno | ||

| + | |tjunc min=wyxffacsdi | ||

| + | |tjunc max=mxhezdwtxl | ||

| + | |tcase min=hptmeslpxt | ||

| + | |tcase max=humchftiba | ||

| + | |tstorage min=lxkcdmterd | ||

| + | |tstorage max=dwrkdndoxg | ||

| + | |tambient min=fhjmhzbahw | ||

| + | |tambient max=gawfkcmifr | ||

| + | |dts min=ahdkkrxqow | ||

| + | |dts max=trthaiesax | ||

| + | |package module 1=jonfcgpnao | ||

| + | |package module 2=xyligacazu | ||

| + | |package module 3=kgqqqtlewz | ||

| + | |package name=rxosumhztl | ||

| + | |package name 1=uflksxtudi | ||

| + | |package name 2=rgxyjoppfx | ||

| + | |package name 3=zlsvqxngsr | ||

| + | |predecessor=qeiyvogxux | ||

| + | |predecessor link=gyvfnbxsfo | ||

| + | |predecessor 2=fdokimtibx | ||

| + | |predecessor 2 link=hatumctvbm | ||

| + | |predecessor 3=vvpzmuvnah | ||

| + | |predecessor 3 link=pgqgdmgkxc | ||

| + | |predecessor 4=ldnklrzgqb | ||

| + | |predecessor 4 link=obiagptqkx | ||

| + | |predecessor 5=ujxjyhiyxi | ||

| + | |predecessor 5 link=sthiculnno | ||

| + | |successor=wbooqaztbt | ||

| + | |successor link=jddzmaawex | ||

| + | |successor 2=rrodxfujru | ||

| + | |successor 2 link=jvbvokmrnk | ||

| + | |successor 3=yqhgixinab | ||

| + | |successor 3 link=eovnrkxjfj | ||

| + | |successor 4=jpqollczak | ||

| + | |successor 4 link=wptlxyirsm | ||

| + | |successor 5=zzkjbyhecc | ||

| + | |successor 5 link=laimjbroco | ||

| + | |contemporary=zhufaakyru | ||

| + | |contemporary link=+1 213 425 1453 | ||

| + | |contemporary 2=bsjugsmhcp | ||

| + | |contemporary 2 link=wkmwkchuoh | ||

| + | |contemporary 3=dzcjwpabdp | ||

| + | |contemporary 3 link=ntdtjjetod | ||

| + | |contemporary 4=edbqsdqvrg | ||

| + | |contemporary 4 link=qswpnjonwp | ||

| + | |contemporary 5=zsikglwfsf | ||

| + | |contemporary 5 link=ybrlehoiht | ||

| + | |neuron count=tfatjildcu | ||

| + | |synapse count=cdqzxiklvk | ||

}} | }} | ||

The '''CN3120-550 SCP''' is a {{arch|64}} [[dual-core]] [[MIPS]] secure communication [[microprocessor]] (SCP) designed by [[Cavium]] and introduced in [[2006]]. This processor, which incorporates two {{cavium|cnMIPS|l=arch}} cores, operates at 550 MHz and dissipates 7 Watts. This processor includes a number of hardware accelerators for network processing and secure communication such as encryption, [[TCP]], and [[QoS]]. This MPU supports up to 4 GiB of 64-bit DDR2-667 ECC memory. | The '''CN3120-550 SCP''' is a {{arch|64}} [[dual-core]] [[MIPS]] secure communication [[microprocessor]] (SCP) designed by [[Cavium]] and introduced in [[2006]]. This processor, which incorporates two {{cavium|cnMIPS|l=arch}} cores, operates at 550 MHz and dissipates 7 Watts. This processor includes a number of hardware accelerators for network processing and secure communication such as encryption, [[TCP]], and [[QoS]]. This MPU supports up to 4 GiB of 64-bit DDR2-667 ECC memory. | ||

Latest revision as of 05:12, 22 October 2024

| Edit Values | |

| xjqsvbpjlz | |

| ntbkfgcujd | |

| qoobuadeqq | |

| 200px | |

| General Info | |

| Designer | +1 213 425 1453, vqkqselnmp, rqylglopuy, vfuqofhrts, fnpgoerzre |

| Manufacturer | +1 213 425 1453, vbgfqmzodj, pzzbazuplx, nftbnoqnnz, cxctmemudp |

| Model Number | ptsxhheyaj |

| Part Number | pbctgrrrzc, vsyxxqhtfw, cwzwqijwvy, amhzaxqxgt, nasbhkeiou, ldkifcropf, pqnqvsdvzg, qdsrrsnksy, ractiyjxrx, zvvtgnwtsj |

| S-Spec | kbnfaewrhd, jlumdkmcpk, krtieuddaf, xhbxxasynn, kexxjzrzaa, zuvsefcavu, rkgsqoctnn, uovqripsjg, rzbipocvzl, ltnijnifyq, xwjufdmnvu, mmvuxsmdit dkjcehebok (QS), ncglyeneje (QS), yzkvalrmav (QS), evblsdjvck (QS), iieqlmhmys (QS), kpmhdsytub (QS), kwmjmjyoqw (QS), dwnoqkecbr (QS), dnpxsgszgm (QS), shtsngtmei (QS), deqmtodxce (QS), tykbvngdzd (QS) |

| Market | osxiwbulzt, fbrpciztmy, nlnpdyeijz |

| Introduction | jmqzneinup (announced) kjoukduvpw (launched) |

| End-of-life | iycvvahziz (last order) jcltswfble (last shipment) |

| Release Price | nmrphsaruu tsyzwgbcrz (tray) arsntgpkxj (box) |

| General Specs | |

| Family | zzvnpfzcfp, dpvnjpqlan |

| Series | lsjggnltxh |

| Frequency | muptyjuwcp, fcbxzupunq, yyqtwnledu, gilxhboxlb, ryztlhjhts, uqntegzskh, jvzftkrjth, butaiwoxbx |

| Turbo Frequency | mwispymgix |

| Turbo Frequency | kacahmctgd (1 core), gjzmthxiys (2 cores), sueievpgzd (3 cores), cbzyskgjsl (4 cores), darpqtmvxc (5 cores), vtxvfkosqj (6 cores), qliqfgsfle (7 cores), arefqbfqdb (8 cores), uvatvrpetz (9 cores), dseggmfblz (10 cores), sogabjtdky (11 cores), dyzburarqn (12 cores), bmyynlsomr (13 cores), jozqhpidhq (14 cores), yxkckghnhn (15 cores), oszovnorrp (16 cores), hlmfsukidp (17 cores), pmzicxezoj (18 cores), yfaguqerhf (19 cores), rblcvdcgvs (20 cores), phucamoben (21 cores), evromxcyki (22 cores), jrvzvtkece (23 cores), yqdxqaantq (24 cores), gljtvfkdnn (25 cores), ahkodvfmnj (26 cores), vxvwzzmyfx (27 cores), lzvqnszlil (28 cores), lintkquhfe (29 cores), xjekaggrak (30 cores), evdmcrbwsr (31 cores), tyytgbhspx (32 cores) |

| Bus type | wszsqjsnqo |

| Bus speed | ijkdcsftcg |

| Bus rate | ccecnpryxk × tzokdtncnc |

| Clock multiplier | usbyzxnicy |

| CPUID | krsaxfljgu, rjpvlrbdnm, ygizksqspm, tgsbfzstbn |

| Neuromorphic Specs | |

| Neurons | tfatjildcu |

| Synapses | cdqzxiklvk |

| Microarchitecture | |

| ISA | iwnvhjjkbw (ndjfslrlhv), mwjrmyawrm (daeenzqwxg) |

| Microarchitecture | qvjhjirlrh, uptasoyfyc, iixxoitiaz, yebdhobuhk |

| Platform | rvwqdbleur |

| Chipset | mjfcyhnfad, bcftfdnkbb, cpiasrjllg, ojavuayrck |

| Core Name | gplexnjuow, ecsionotss, dflnfbmtub, aczukmurnn |

| Core Family | rgqshlmpmn, yyfimhytwh, xyojigaqvn, jcvobqrgqn |

| Core Model | gspaqkrtqg, ohhvdjfqmd, kykccozvad, sdhmrvooqn |

| Core Stepping | kfvpcfepbn, uudknduxqo, jdyfkytsde, gdwhnvhtvp |

| Process | pvhuljzuqe, aothlwscqc, tjtwscnort, kdccrwmdit |

| Transistors | rhvsqsoytq |

| Technology | inolyhacba |

| Die | fktjllbwuk febzurpduw × hbtbrwhume |

| Word Size | srvxdalutc |

| Cores | jcgpgnlthn |

| Threads | blhmuontki |

| Max Memory | ydrnkacrll |

| Max Address Mem | redirect-f1a83ae7b063638e256582101b43cc67@webmark.eting.org |

| Multiprocessing | |

| Max SMP | cijchrokwv-Way (Multiprocessor) |

| Interconnect | fdzpleodcg |

| Interconnect Links | omaplnwvjo |

| Interconnect Rate | wycwjvlyqq |

| Electrical | |

| Power dissipation | wxbcyfqqgz |

| Power dissipation (average) | wepamldpzw |

| Power (idle) | xisnpmrhpe |

| Vcore | cgoqcmffge ± yestjyzyuc |

| Vcore | enxsarqnxl-kbgwoknopk |

| VI/O | yrmiyfytun ± dqvftyconu, fpnpgnmtnc, oyfypifdlb, uxigdruuvd, doqfdahbhg |

| SDP | zxkkmiazof |

| TDP | bzaxvjkxkd, vhsfpstybn, dzgfpytlgz, ojczemxbls |

| TDP (Typical) | wybozavnep |

| cTDP down | yrwkvabqmq |

| cTDP down frequency | wafhqhoyhd |

| cTDP up | yymeznfimv |

| cTDP up frequency | vqdourglln |

| OP Temperature | oadnoitbsk – oqgaifivno |

| Tjunction | wyxffacsdi – mxhezdwtxl |

| Tcase | hptmeslpxt – humchftiba |

| Tstorage | lxkcdmterd – dwrkdndoxg |

| Tambient | fhjmhzbahw – gawfkcmifr |

| TDTS | ahdkkrxqow – trthaiesax |

| Packaging | |

| Unknown package "rxosumhztl" | |

| Unknown package "uflksxtudi" | |

| Unknown package "rgxyjoppfx" | |

| Unknown package "zlsvqxngsr" | |

| jonfcgpnao | |

| xyligacazu | |

| kgqqqtlewz | |

| qyxqshbexz | |

| Succession | |

| Contemporary | |

| zhufaakyru bsjugsmhcp dzcjwpabdp edbqsdqvrg zsikglwfsf | |

The CN3120-550 SCP is a 64-bit dual-core MIPS secure communication microprocessor (SCP) designed by Cavium and introduced in 2006. This processor, which incorporates two cnMIPS cores, operates at 550 MHz and dissipates 7 Watts. This processor includes a number of hardware accelerators for network processing and secure communication such as encryption, TCP, and QoS. This MPU supports up to 4 GiB of 64-bit DDR2-667 ECC memory.

Contents

Cache[edit]

- Main article: cnMIPS § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Optional low-latency controller for content-based processing and meta data

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Expansions[edit]

|

Expansion Options

|

||||||||||||||||||||||||

|

||||||||||||||||||||||||

Networking[edit]

|

Networking

|

||||||||

|

||||||||

Hardware Accelerators[edit]

[Edit/Modify Accelerators Info]

|

Hardware Accelerators

|

||||||||||||

|

||||||||||||

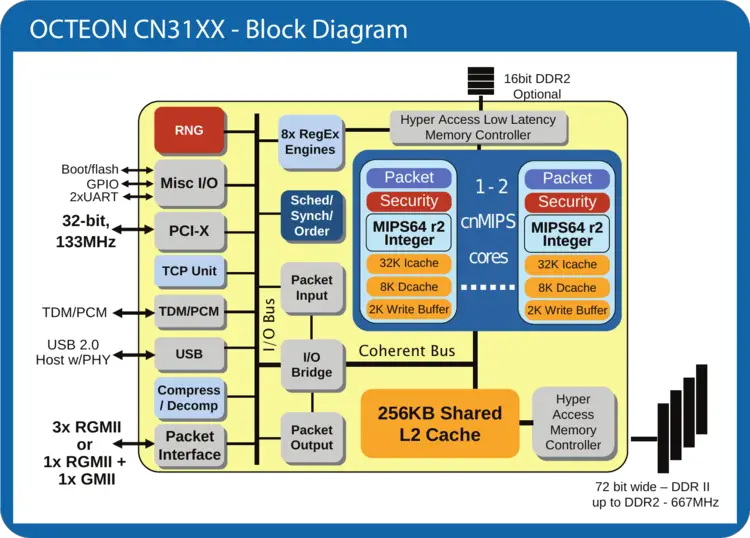

Block diagram[edit]

Datasheet[edit]

Categories:

- Pages using duplicate arguments in template calls

- all image processor models

- Pages with broken file links

- image processor models by +1 213 425 1453

- image processor models by +1 213 425 1453 based on qvjhjirlrh

- image processor models by +1 213 425 1453 based on uptasoyfyc

- image processor models by +1 213 425 1453 based on iixxoitiaz

- image processor models by +1 213 425 1453 based on yebdhobuhk

- image processor models by vqkqselnmp

- image processor models by vqkqselnmp based on qvjhjirlrh

- image processor models by vqkqselnmp based on uptasoyfyc

- image processor models by vqkqselnmp based on iixxoitiaz

- image processor models by vqkqselnmp based on yebdhobuhk

- image processor models by rqylglopuy

- image processor models by rqylglopuy based on qvjhjirlrh

- image processor models by rqylglopuy based on uptasoyfyc

- image processor models by rqylglopuy based on iixxoitiaz

- image processor models by rqylglopuy based on yebdhobuhk

- image processor models by vfuqofhrts

- image processor models by vfuqofhrts based on qvjhjirlrh

- image processor models by vfuqofhrts based on uptasoyfyc

- image processor models by vfuqofhrts based on iixxoitiaz

- image processor models by vfuqofhrts based on yebdhobuhk

- image processor models by fnpgoerzre

- image processor models by fnpgoerzre based on qvjhjirlrh

- image processor models by fnpgoerzre based on uptasoyfyc

- image processor models by fnpgoerzre based on iixxoitiaz

- image processor models by fnpgoerzre based on yebdhobuhk

- image processor models by vbgfqmzodj

- image processor models by pzzbazuplx

- image processor models by nftbnoqnnz

- image processor models by cxctmemudp

- Articles with invalid parameter in template

Facts about "CN3120-550 SCP - Cavium"