From WikiChip

Difference between revisions of "amd/k6-2/k6-2-333afr"

m (Bot: moving all {{mpu}} to {{chip}}) |

|||

| (9 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{amd title|K6-2/333AFR}} | {{amd title|K6-2/333AFR}} | ||

| − | {{ | + | {{chip |

| name = K6-2/333AFR | | name = K6-2/333AFR | ||

| − | | no image = | + | | no image = |

| − | | image = | + | | image = Ic-photo-AMD--AMD-K6-2 333AFR-(K6-2-CPU).png |

| image size = | | image size = | ||

| − | | caption = | + | | caption = Week 30, 1998 |

| designer = AMD | | designer = AMD | ||

| manufacturer = AMD | | manufacturer = AMD | ||

| model number = K6-2/333AFR | | model number = K6-2/333AFR | ||

| − | | part number = K6-2/333AFR | + | | part number = AMD-K6-2/333AFR |

| − | |||

| part number 2 = | | part number 2 = | ||

| part number 3 = | | part number 3 = | ||

| + | | part number 4 = | ||

| market = Desktop | | market = Desktop | ||

| first announced = May 28, 1998 | | first announced = May 28, 1998 | ||

| Line 47: | Line 47: | ||

| thread count = 1 | | thread count = 1 | ||

| max cpus = 1 | | max cpus = 1 | ||

| − | | max memory = 4 | + | | max memory = 4 GiB |

| + | |||

| − | |||

| power = 19 W | | power = 19 W | ||

| v core = 2.2 V | | v core = 2.2 V | ||

| Line 83: | Line 83: | ||

== Cache == | == Cache == | ||

{{main|amd/microarchitectures/k6-2#Memory_Hierarchy|l1=K6-2 § Cache}} | {{main|amd/microarchitectures/k6-2#Memory_Hierarchy|l1=K6-2 § Cache}} | ||

| − | [[L2$]] can be 512 | + | [[L2$]] can be 512 KiB to 2 MiB, depending on manufacturer and [[motherboard]] model. L2$ is off-chip. |

{{cache info | {{cache info | ||

| − | |l1i cache=32 | + | |l1i cache=32 KiB |

| − | |l1i break=1x32 | + | |l1i break=1x32 KiB |

|l1i desc=2-way set associative | |l1i desc=2-way set associative | ||

|l1i extra= | |l1i extra= | ||

| − | |l1d cache=32 | + | |l1d cache=32 KiB |

| − | |l1d break=1x32 | + | |l1d break=1x32 KiB |

|l1d desc=2-way set associative | |l1d desc=2-way set associative | ||

|l1d extra= | |l1d extra= | ||

| Line 107: | Line 107: | ||

== Features == | == Features == | ||

| − | {{ | + | {{x86 features |

| mmx = true | | mmx = true | ||

| 3dnow = true | | 3dnow = true | ||

| Line 113: | Line 113: | ||

* Auto-power down state | * Auto-power down state | ||

* Stop clock state | * Stop clock state | ||

| + | |||

| + | == Gallery == | ||

| + | <gallery> | ||

| + | File:Ic-photo-amd-AMD-K6-2-333AFR.png|Week 30, 1998 | ||

| + | </gallery> | ||

| + | |||

| + | == Documents == | ||

| + | |||

| + | === DataSheet === | ||

| + | * [[:File:AMD-K6-2 Processor Data Sheet (February, 2000).pdf|AMD-K6-2 Processor Data Sheet]]; Publication #21850 Revision J/0, February 2000 | ||

Latest revision as of 15:08, 13 December 2017

| Edit Values | |

| K6-2/333AFR | |

| |

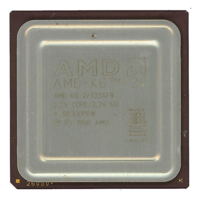

| Week 30, 1998 | |

| General Info | |

| Designer | AMD |

| Manufacturer | AMD |

| Model Number | K6-2/333AFR |

| Part Number | AMD-K6-2/333AFR |

| Market | Desktop |

| Introduction | May 28, 1998 (announced) June 4, 1998 (launched) |

| Shop | Amazon |

| General Specs | |

| Family | K6-2 |

| Series | K6-2 Desktop |

| Frequency | 333.66 MHz |

| Bus type | FSB |

| Bus speed | 95.33 MHz |

| Bus rate | 95.33 MT/s |

| Clock multiplier | 3.5 |

| CPUID | 580, 58C |

| Microarchitecture | |

| Microarchitecture | K6-2 |

| Platform | Super 7 |

| Core Name | Chomper, Chomper Extended |

| Core Family | 5 |

| Core Model | 8 |

| Core Stepping | 0, 12 |

| Process | 0.25 µm |

| Transistors | 9,300,000 |

| Technology | CMOS |

| Die | 81 mm² |

| Word Size | 32 bit |

| Cores | 1 |

| Threads | 1 |

| Max Memory | 4 GiB |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Power dissipation | 19 W |

| Vcore | 2.2 V ± 0.1 V |

| VI/O | 3.3675 V ± 7% |

| Tcase | 0 °C – 70 °C |

| Tstorage | -65 °C – 150 °C |

K6-2/333AFR was a 32-bit x86 K6-2-based microprocessor designed and manufactured in 1998 by AMD. Manufactured using a 0.25 µm process, this MPU operated at 333 MHz with a FSB of 95 MHz consumed 19 W. Note that K6-2/333AFR-66 is an identical model with a multiplier of 5 instead of 3.6 designed to support a 66 MHz bus instead.

Cache[edit]

- Main article: K6-2 § Cache

L2$ can be 512 KiB to 2 MiB, depending on manufacturer and motherboard model. L2$ is off-chip.

| Cache Info [Edit Values] | ||

| L1I$ | 32 KiB 32,768 B 0.0313 MiB |

1x32 KiB 2-way set associative |

| L1D$ | 32 KiB 32,768 B 0.0313 MiB |

1x32 KiB 2-way set associative |

Graphics[edit]

This SoC has no integrated graphics processing unit.

Features[edit]

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||

|

||||

- Auto-power down state

- Stop clock state

Gallery[edit]

Documents[edit]

DataSheet[edit]

- AMD-K6-2 Processor Data Sheet; Publication #21850 Revision J/0, February 2000

Facts about "K6-2/333AFR - AMD"

| l1d$ description | 2-way set associative + |

| l1i$ description | 2-way set associative + |