From WikiChip

Difference between revisions of "intel/xeon e7/e7-4870"

m (Bot: corrected param) |

|||

| Line 10: | Line 10: | ||

| model number = E7-4870 | | model number = E7-4870 | ||

| part number = AT80615007263AA | | part number = AT80615007263AA | ||

| − | | part number | + | | part number 2 = BX80615E74870 |

| − | |||

| part number 3 = | | part number 3 = | ||

| + | | part number 4 = | ||

| market = Server | | market = Server | ||

| first announced = April 5, 2011 | | first announced = April 5, 2011 | ||

Revision as of 18:50, 30 June 2017

Template:mpu Xeon E7-4870 is a 64-bit deca-core x86 data center microprocessor that supports up to 4 sockets. This first generation Xeon E7 processor, Westmere-based, operates at a base frequency of 2.4 GHz with turbo frequency of 2.8 GHz for 2 active cores. This chip has a TDP of 130 W, supporting up to 4 channels of DDR3 with support of up to 2 TB of memory.

Cache

- Main article: Westmere § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Graphics

This SoC has no integrated graphics processing unit.

Memory controller

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||

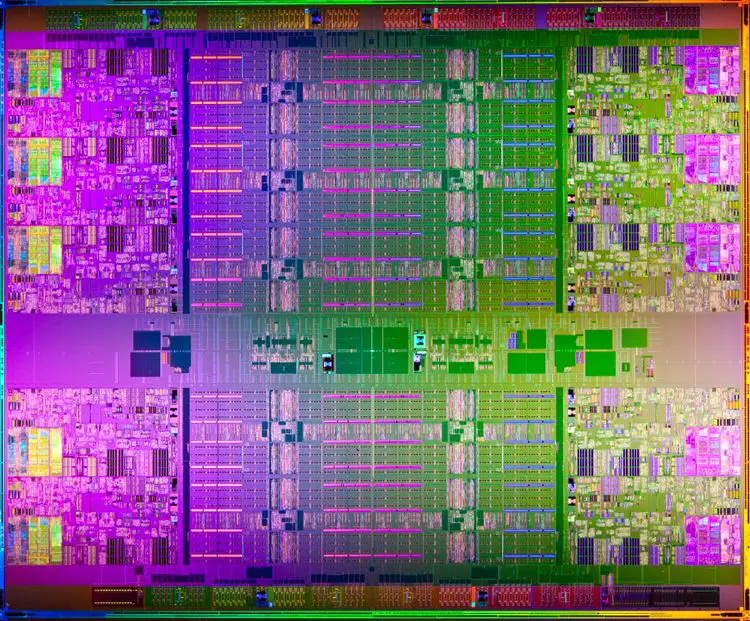

Die Shot

- 513 mm²

- 2,600,000,000 transistors

- 10 cores

Facts about "Xeon E7-4870 - Intel"

| has ecc memory support | true + |

| has extended page tables support | true + |

| has feature | Advanced Encryption Standard Instruction Set Extension +, Hyper-Threading Technology +, Turbo Boost Technology 1.0 +, Enhanced SpeedStep Technology +, Trusted Execution Technology +, Intel VT-x +, Intel VT-d + and Extended Page Tables + |

| has intel enhanced speedstep technology | true + |

| has intel trusted execution technology | true + |

| has intel turbo boost technology 1 0 | true + |

| has intel vt-d technology | true + |

| has intel vt-x technology | true + |

| has second level address translation support | true + |

| has simultaneous multithreading | true + |

| has x86 advanced encryption standard instruction set extension | true + |

| l1$ size | 640 KiB (655,360 B, 0.625 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 320 KiB (327,680 B, 0.313 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 320 KiB (327,680 B, 0.313 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 2.56 MiB (2,621.44 KiB, 2,684,354.56 B, 0.0025 GiB) + |

| l3$ description | 16-way set associative + |

| l3$ size | 30 MiB (30,720 KiB, 31,457,280 B, 0.0293 GiB) + |

| max memory bandwidth | 31.77 GiB/s (32,532.48 MiB/s, 34.113 GB/s, 34,112.778 MB/s, 0.031 TiB/s, 0.0341 TB/s) + |

| max memory channels | 4 + |

| supported memory type | DDR3-1066 + |