From WikiChip

Difference between revisions of "intel/core i7ee/i7-4960x"

m (Bot: corrected mem) |

m (Bot: corrected mem) |

||

| Line 106: | Line 106: | ||

| bandwidth schan = | | bandwidth schan = | ||

| bandwidth dchan = | | bandwidth dchan = | ||

| − | | max memory = 64 | + | | max memory = 64 GiB |

}} | }} | ||

Revision as of 06:01, 23 June 2017

Template:mpu The Core i7-4960X Extreme Edition is a 64-bit hexa-core top-of-the-line MPU introduced by Intel for the enthusiasts market. The i7-4960X served as Intel's flagship microprocessor for the Ivy Bridge microarchitecture - it was superseded by the Haswell-based i7-5960X MPU. Operating at 3.6 GHz with turbo frequency of 4 GHz for a single core, this chip supports 64 GB of memory (DDR3) and has a TDP of 130 Watts.

Cache

- Main article: Ivy Bridge's Cache

| Cache Info [Edit Values] | ||

| L1I$ | 192 KiB 196,608 B 0.188 MiB |

6x32 KiB 8-way set associative (per core) |

| L1D$ | 192 KiB 196,608 B 0.188 MiB |

6x32 KiB 8-way set associative (per core) |

| L2$ | 1,536 KiB 1.5 MiB 1,572,864 B 0.00146 GiB |

6x256 KiB 8-way set associative (per core) |

| L3$ | 15 MiB 15,360 KiB 15,728,640 B 0.0146 GiB |

20-way set associative (shared) |

Graphics

This SoC has no integrated graphics processing unit.

Memory controller

| Integrated Memory Controller | |

| Type | DDR3-1066, DDR3-1333, DDR3-1600, DDR3-1866 |

| Controllers | 1 |

| Channels | 4 |

| ECC Support | No |

| Max bandwidth | 59.7 GB/s |

| Max memory | 64 GiB |

Expansions

Features

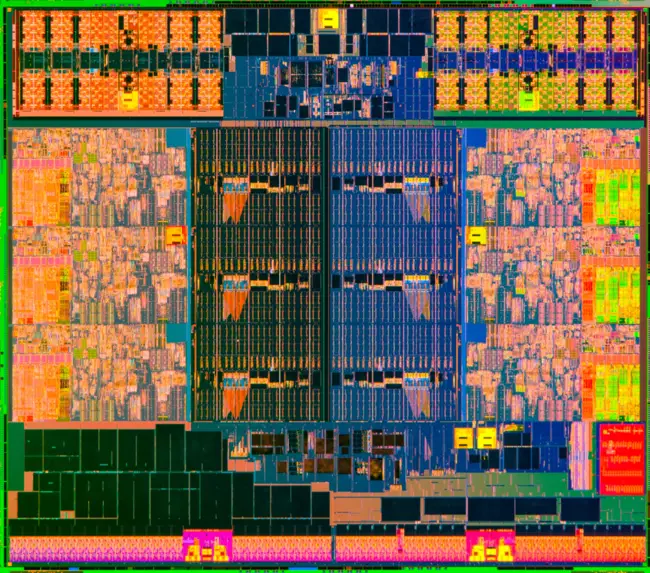

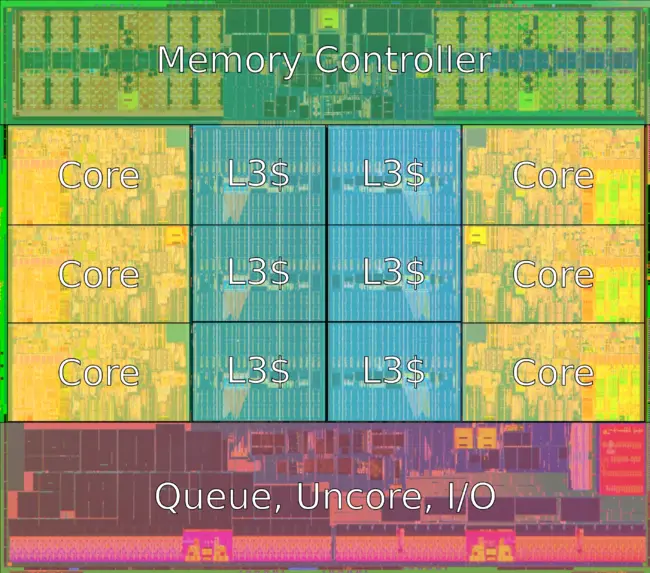

Die Shot

- 22 nm process

- 1,860,000,000 transistors

- 256.5 mm²

- 15.0 mm x 17.1 mm

See also

Facts about "Core i7-4960X Extreme Edition - Intel"

| l1d$ description | 8-way set associative + |

| l1d$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l1i$ description | 8-way set associative + |

| l1i$ size | 192 KiB (196,608 B, 0.188 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 1.5 MiB (1,536 KiB, 1,572,864 B, 0.00146 GiB) + |

| l3$ description | 20-way set associative + |

| l3$ size | 15 MiB (15,360 KiB, 15,728,640 B, 0.0146 GiB) + |