From WikiChip

Difference between revisions of "amd/ryzen 7/1700"

| Line 80: | Line 80: | ||

| package module 1 = {{packages/amd/socket am4}} | | package module 1 = {{packages/amd/socket am4}} | ||

}} | }} | ||

| − | '''Ryzen 7 1700''' is a {{arch|64}} [[octa-core]] high-end performance [[x86]] desktop microprocessor introduced by [[AMD]] in early [[2017]]. This processor is based on AMD's {{amd|Zen|Zen microarchitecture|l=arch}} and is fabricated on a [[14 nm process]]. The 1700 operates at a base frequency of 3 GHz with a [[TDP]] of 65 W and a {{amd|Precision Boost|Boost}} frequency of 3.7 GHz. This MPU supports up to 64 | + | '''Ryzen 7 1700''' is a {{arch|64}} [[octa-core]] high-end performance [[x86]] desktop microprocessor introduced by [[AMD]] in early [[2017]]. This processor is based on AMD's {{amd|Zen|Zen microarchitecture|l=arch}} and is fabricated on a [[14 nm process]]. The 1700 operates at a base frequency of 3 GHz with a [[TDP]] of 65 W and a {{amd|Precision Boost|Boost}} frequency of 3.7 GHz. This MPU supports up to 64 GiB of dual-channel non-ECC DDR4-2400 memory. |

== Cache == | == Cache == | ||

Revision as of 17:27, 2 March 2017

Template:mpu Ryzen 7 1700 is a 64-bit octa-core high-end performance x86 desktop microprocessor introduced by AMD in early 2017. This processor is based on AMD's Zen microarchitecture and is fabricated on a 14 nm process. The 1700 operates at a base frequency of 3 GHz with a TDP of 65 W and a Boost frequency of 3.7 GHz. This MPU supports up to 64 GiB of dual-channel non-ECC DDR4-2400 memory.

Cache

- Main article: Zen § Cache

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||

Memory controller

|

Integrated Memory Controller

|

||||||||||||||

|

||||||||||||||

Expansions

|

Expansion Options

|

||||||||

|

||||||||

Graphics

This processor has no integrated graphics.

Features

[Edit/Modify Supported Features]

|

Supported x86 Extensions & Processor Features

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

Shop

<amazon type="simple-listing1" search-title="AMD Ryzen 7 1700" search-phrase="AMD Ryzen 7 1700" />

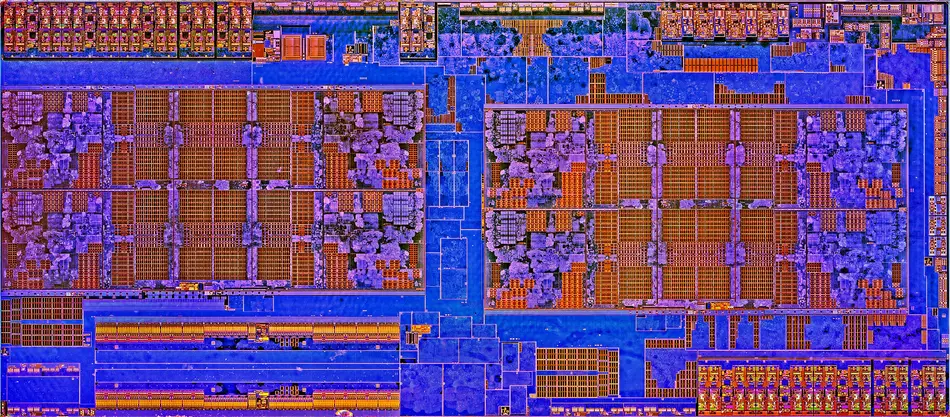

Die Shot

- See also: Zen § Die Shot

- 14 nm process

- 12 metal layers

- 2,000 meters of signals

- 4,800,000,000 transistors

- ~195 mm²

Facts about "Ryzen 7 1700 - AMD"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Ryzen 7 1700 - AMD#io + |

| has advanced vector extensions | true + |

| has advanced vector extensions 2 | true + |

| has ecc memory support | false + |

| has feature | Advanced Vector Extensions +, Advanced Vector Extensions 2 + and Advanced Encryption Standard Instruction Set Extension + |

| has x86 advanced encryption standard instruction set extension | true + |

| l1$ size | 768 KiB (786,432 B, 0.75 MiB) + |

| l1d$ description | 8-way set associative + |

| l1d$ size | 256 KiB (262,144 B, 0.25 MiB) + |

| l1i$ description | 4-way set associative + |

| l1i$ size | 512 KiB (524,288 B, 0.5 MiB) + |

| l2$ description | 8-way set associative + |

| l2$ size | 4 MiB (4,096 KiB, 4,194,304 B, 0.00391 GiB) + |

| l3$ description | 16-way set associative + |

| l3$ size | 16 MiB (16,384 KiB, 16,777,216 B, 0.0156 GiB) + |

| max memory bandwidth | 35.76 GiB/s (36,618.24 MiB/s, 38.397 GB/s, 38,397.008 MB/s, 0.0349 TiB/s, 0.0384 TB/s) + |

| max memory channels | 2 + |

| max pcie lanes | 20 + |

| supported memory type | DDR4-2400 + |