From WikiChip

Difference between revisions of "graphcore/microarchitectures/colossus"

| Line 18: | Line 18: | ||

== Architecture == | == Architecture == | ||

{{empty section}} | {{empty section}} | ||

| + | |||

| + | == Die == | ||

| + | === Floorplan === | ||

| + | * [[16 nm process]] | ||

| + | * ~800 mm² die size | ||

| + | * 23,647,173,309 transistors | ||

| + | * 1,216 FPUs | ||

| + | ** 300 MiB on-die memory | ||

| + | |||

| + | :[[File:colossus floorplan.png|500px]] | ||

Revision as of 02:09, 24 June 2018

| Edit Values | |

| Colossus µarch | |

| General Info | |

| Arch Type | NPU |

| Designer | Graphcore |

| Manufacturer | TSMC |

| Introduction | 2018 |

| Process | 16 nm |

Colossus is a 16 nm microarchitecture for high-performance neural processors designed by Graphcore set to be introduced in late-2018.

Etymology

Codename Colossus was chosen in honor of Tommy Flowers and the Colossus computer.

Process Technology

Colossus is designed to be fabricated on TSMC's 16 nm FinFET process.

Architecture

| This section is empty; you can help add the missing info by editing this page. |

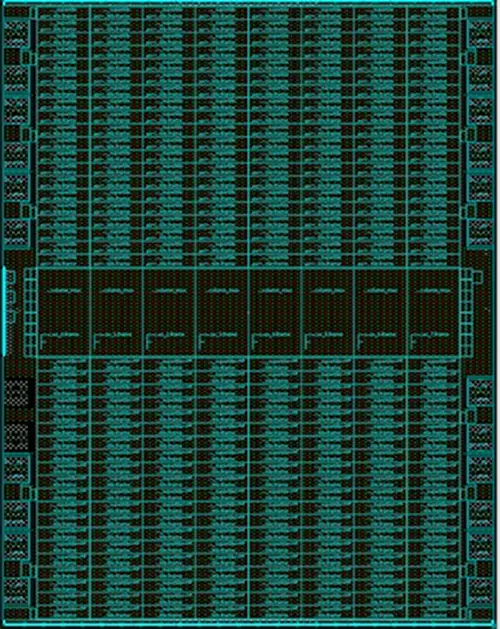

Die

Floorplan

- 16 nm process

- ~800 mm² die size

- 23,647,173,309 transistors

- 1,216 FPUs

- 300 MiB on-die memory

Facts about "Colossus - Graphcore"

| codename | Colossus + |

| designer | Graphcore + |

| first launched | 2018 + |

| full page name | graphcore/microarchitectures/colossus + |

| instance of | microarchitecture + |

| manufacturer | TSMC + |

| name | Colossus + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |