The technology node (also process node, process technology or simply node) refers to a specific semiconductor manufacturing process and its design rules. Different nodes often imply different circuit generations and architectures. Generally, the smaller the technology node means the smaller the feature size, producing smaller transistors which are both faster and more power-efficient. Historically, the process node name referred to a number of different features of a transistor including the gate length as well as M1 half-pitch. Most recently, due to various marketing and discrepancies among foundries, the number itself has lost the exact meaning it once held. Recent technology nodes such as 22 nm, 16 nm, 14 nm, and 10 nm refer purely to a specific generation of chips made in a particular technology. It does not correspond to any gate length or half pitch. Nevertheless, the name convention has stuck and it's what the leading foundries call their nodes.

In 2017 node names has been entirely overtaken by marketing, some of the leading-edge foundries began giving all improved nodes a new name, regardless of whether or not the node has had any kind of transistor shrink or metallization stack scaling. Various enhancements have been announced: "12nm", "11nm", "9nm", "8nm", "6nm", and "4nm". Intel also introduces new enhanced processes nodes but they maintain a consistent naming scheme (e.g., "14nm", "14nm+", "14nm++") while reserving the 'common' node names for actual 0.7x shrinks (e.g., "14nm", "10nm", "7nm").

Nomenclature

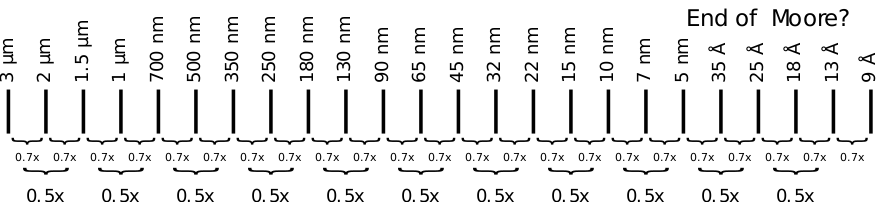

The driving force behind process node scaling is Moore's Law. To achieve density doubling, the contacted poly pitch (CPP) and the minimum metal pitch (MMP) need to scale by roughly 0.7x each node. In other words, a scaling of 0.7x CPP ⋅ 0.7x MMP ≈ ½ area. The node names are effectively a self-fulfilling prophecy driven by Moore's Law.

History

Roughly for the first 35 years of the semiconductor history, since the first mass production of MOSFET in the 1960s to the late 1990s, the process node more or less referred to the transistor's gate length (Lg) which was also considered the "minimum feature size". For example, Intel's 0.5 µm process had Lg = 0.5 µm. This lasted until the 0.25 µm process in 1997 at which point Intel started introducing more aggressive gate length scaling. For example, their 0.25 µm process had Lg = 0.20 µm and likewise, their 0.18 µm process had Lg = 0.13 µm (a node ahead). At those nodes the "process node" was effectively larger than the gate length.

The term itself, as we know it today, dates back to the 1990s where microprocessors development was driven by higher frequency while DRAM development was dominated by the evergrowing demand for higher capacities. Since higher capacities were achieved through higher density, it was DRAM that became the driver of technology scaling. This continued to be the case well into the 2000s. The International Technology Roadmap for Semiconductors (ITRS) provides the semiconductor industry with guidance and assistance with various technology nodes. By 2006, as microprocessors started dominating the technology scaling, ITRS replaced the term with a number of separate indicators for Flash, DRAM, and MPU/ASIC.

The ITRS traditionally defined the process node as the smallest half-pitch of contacted metal 1 lines allowed in the fabrication process. It is a common metric used to describe and differentiate the technologies used in fabricating integrated circuits.

Meaning lost

At the 45 nm process, Intel reached a gate length of 25 nm on a traditional planar transistor. At that node the gate length scaling effectively stalled; any further scaling to the gate length would produce less desirable results. Following the 32 nm process node, while other aspects of the transistor shrunk, the gate length was actually increased.

With the introduction of FinFET by Intel in their 22 nm process, the transistor density continued to increase all while the gate length remained more or less a constant. This is due to the properties of FinFET; for example the effective channel length is a function of the new fins (Weff = 2 * Hfin + Wfin). Due to how the transistor changed dramatically from how it used to be, the current naming scheme lost any meaning.

Half node

Half node, much like the process term also dates to the 1990s when incremental shrinkage was readily achievable. A full technology node was expected to have a linear scaling shrink of 0.7x (e.g. 130 nm after a full shrink yields 90 nm). Similarly, the associated half node was then expected to have a 0.9x linear shrink. The premise of this idea is that when a new technology node was being considered for a new full node, foundries design rules (e.g. standard cells) were carefully designed with the expectation that a half node shrink was to follow after 18 months. When a half shrink finally took place, it was just a matter of various readjustments. Proper planning and proactive considerations during circuit design stages could allow seamless transition to the new process without encountering design rule violations, timing, or otherwise any reliability issues. Note that some steps such as packaging do need to be redesigned.

Leading edge trend

As shrinking becomes more complex, requiring more capital, expertise, and resources, the number of companies capable of providing leading edge fabrication has been steadily dropping. As of 2018, only four companies are now capable of fabricating integrated circuits on the most cutting edge process: Intel, Samsung, TSMC, and GlobalFoundries.

| Number of Foundries with a Cutting Edge Logic Fab | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

|

SilTerra |

ADI |

Cypress |

Renesas (NEC) |

Renesas (NEC) |

Panasonic |

IBM |

GlobalFoundries |

Samsung |

GlobalFoundries |

Future |

| 180 nm | 130 nm | 90 nm | 65 nm | 45 nm/40 nm | 32 nm/28 nm | 22 nm/20 nm | 16 nm/14 nm | 10 nm | 7 nm | 5 nm |

Semiconductor lithography processes technology

Semiconductor lithography processes technology