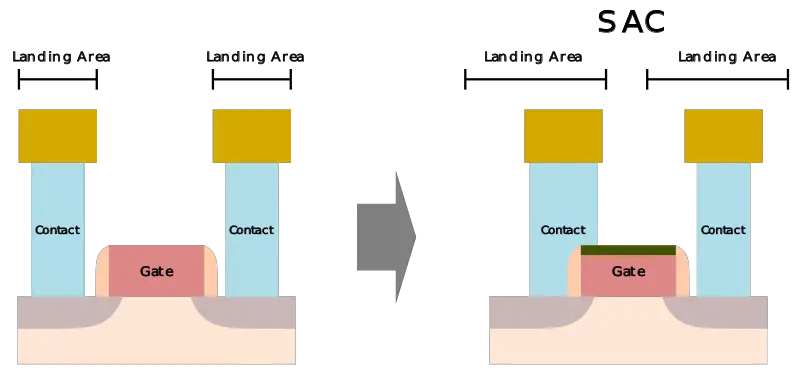

Self-Aligned Contact (SAC) is a semiconductor process flow technique that adds a protective dielectric layer over the transistor gate in order to prevent contact-to-gate shorts. SAC is used to enable aggressive scaling of the contacted poly pitch while minimizing yield loss due to misalignment and partial overlaps of the contacts over the gate.

Overview

On recent leading-edge nodes, the gate length no longer scales are much as they historically used to. Despite that slowdown, the contacted poly pitch continues to scale. The total working spaces include the area for the contacts, the gate length, and the two spacers. Unfortunately, since the gate length no longer scales as much as the CPP, the space length for the contacts is decreasing sharply. The trend is not sustainable and eventually, there was a need to be able to length much closer to the gate and even on top of the gate. In addition to the lack of space, problems with landing the contacts are exasperated by the tighter alignment tolerances and overlay issues due to multiple masks (e.g., SADP, SAQP).

The compounding issues have meant the industry needed to move to a self-aligned contact scheme. Under the self-aligned contact (SAC) flow, it's now possible to land the contacts much closer or even on top of the gate without creating a shot. This meant the contact poly pitch can continue to scale all while relaxing the alignment tolerances which means high die yield.

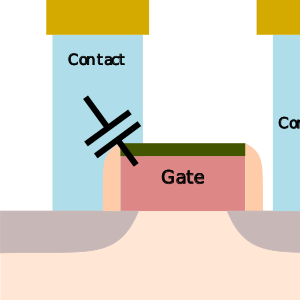

A downside to using SAC is that the gate-SD contact capacitance increases significantly due to the lack of distance between the two which are now only separated by a smaller spacer material.

Industry

Memory

SAC has been used for over a decade in memory prior to its introduction in logic in both flash and DRAM.

Intel

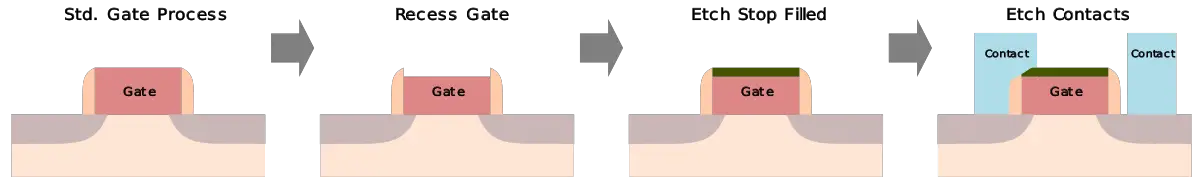

Intel introduced SAC along with the first high-volume FinFET process at their 22 nm process node. Three new steps were introduced. The flow is as follow.

- Intel's standard process is used to form the gate metal

- The gate electrode is recessed

- The recessed area is filled with silicon nitride etch stop & polish

- Capping oxide

- Contact patterning

Following their standard process for forming the metal gate and after it has been planarized, the gate is recessed back. The silicon nitride etch stop is then deposited and planarized forming an isolation layer followed by a capping oxide layer. Finally, the contact etching can then follow, allowing contacts to land directly on the gate without causing a shot.

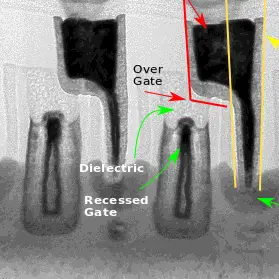

The TEM below, taken by Intel, shows contacts that were intentionally overlaid on the gate, demonstrating the contacts can land on or near the gate due to misalignment and still work as desired.

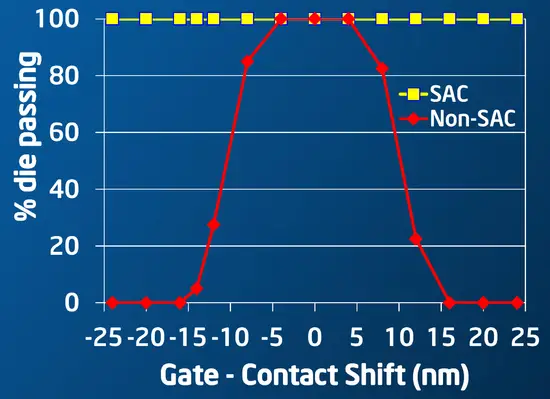

Without SAC, for their 22 nm process, Intel reports a contact landing misalignment of roughly ± 5 nm. A misalignment of up to ± 10nm drops the yield of passing dies down to close to 80% with anything higher drops the yield sharply. With SAC, no yield loss is observed due to contact misalignment which extends the tolerance to as much as ± 25 nm.

See also

Bibliography

- Intel, SEMICON West 2012.

- Intel, 2012 Symposia on VLSI Technology and Circuits (VLSI 2012).