(→Brands) |

|||

| Line 145: | Line 145: | ||

== Bibliography == | == Bibliography == | ||

| − | * {{ | + | * {{bib|hc|27|Phytium}} |

Revision as of 16:37, 15 October 2019

| Edit Values | |

| Xiaomi µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Phytium |

| Manufacturer | TSMC |

| Introduction | 2017 |

| Process | 28 nm |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | ARMv8 |

| Cache | |

| L1I Cache | 32 KiB/Core |

| L1D Cache | 32 KiB/Core |

| L2 Cache | 4 MiB/Panel |

| L3 Cache | 16 MiB/CMC |

| Cores | |

| Core Names | FTC660, FTC661, FTC662 |

Xiaomi is an ARM microarchitecture designed in-house by Phytium for their consumer market and server-based microprocessors.

Contents

Brands

| Codename | Brand | Description |

|---|---|---|

| Mars | FT-2000 FT-2000+ |

|

| Earth | FT-1500A |

|

Architecture

Overview

- Fully ARMv8 compatible

- Support AArch32 and AArch64 modes

- EL0-EL3 supported

- ASIMD-128

- 28 nm process

- Scalable design

- 4 to 64 cores

- Mesh topology network-on-chip

- Panel-based (grid) architecture

- Global cache coherency

- 2x DDR3-1600 channels per panel

- ECC support

- 2x 16-lane PCIe 3.0

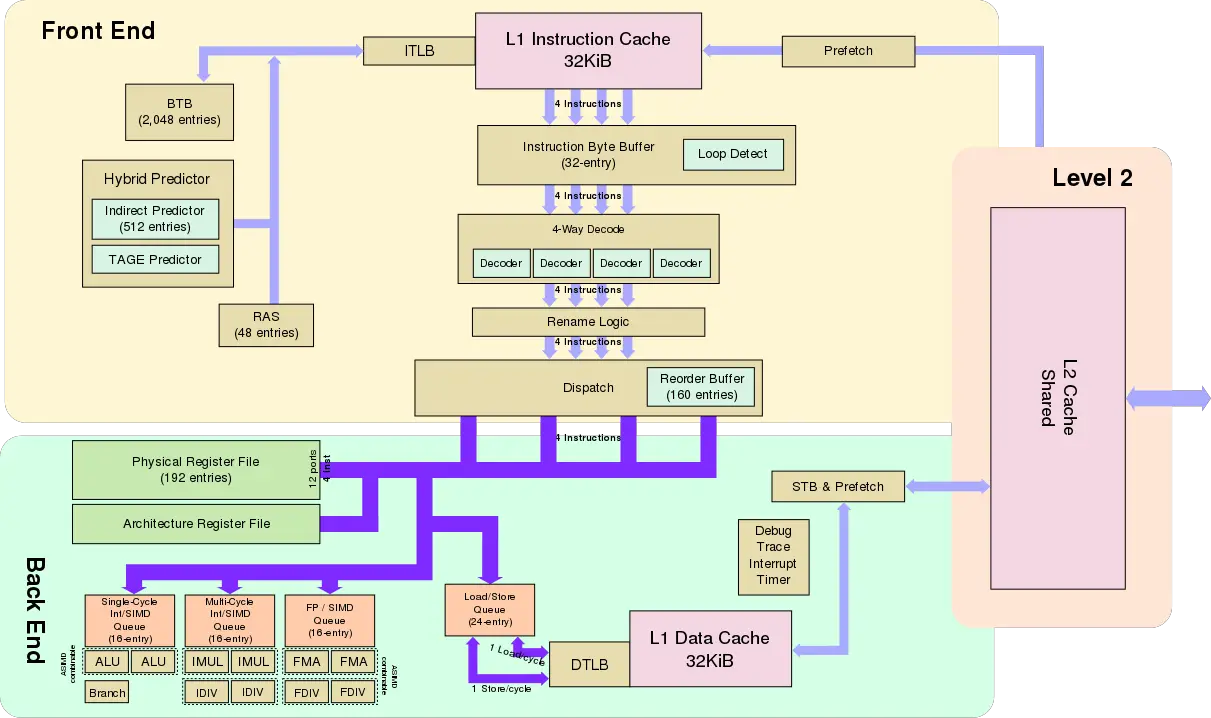

Block Diagram

Memory Hierarchy

- Cache

Pipeline

Each Xiaomi core is an ARMv8-compatible core implemented as a superscalar, out-of-order, 4-decode/4-dispatch pipeline with a hybrid branch prediction.

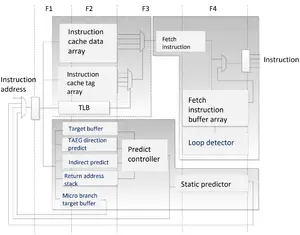

Front End

The front-end consists of the instruction caches & prefetches, fetching of instructions, and decoding. Xiaomi cores contain a 32 KiB L1 instruction cache with a prefetcher designed to reduce caches misses. On hits, 2 cycles are required for retrieval of instructions from the L1. Xiaomi has a hybrid branch predictor made of a TAGE predictor and a 512-entry indirect predictor. The BP unit also has a 48-entry Return Address Stack (RAS) for speculative subroutine return and a 2K-entry BTB. Up to four instructions can be fetches each cycle into the instruction buffer which is 32 entries in size.

The buffer is also a loop detection buffer, responsible for detecting loop patterns and hold them in the instruction buffer, bypassing the cache so they can be sent directly to decode. From the instruction buffer, up to four instructions can be decoded each cycle, up to four instructions can be renamed each cycle, and up to four instructions can be dispatched each cycle. Everything is done in-order up to this point.

Back End

The back-end performs operations out-of-order for the most part and is in charge of queuing instructions, executing them and retiring them. Dispatch contains a 160-entry ReOrder Buffer (ROB) and can dispatch up to 4 instructions per cycle. Note that over 210 instructions can be in-flight throughout the entire pipeline. Operand values can be read from Xiaomi's physical register file and an architectural register file in order to remove the various dependencies. Registers are only updated from the physical register file to the architectural register file when the corresponding instructions require. The physical register file contains 192 physical registers supporting up to four parallel instruction reads. Because ARM has instructions with up to four operands, the register file would need 16 ports to support those simultaneous instructions. To reduce some of the complexity, Phytium chose to reduce the number of ports to 12 where some of the ports are dedicated to each instruction and others are multiplexed. Phytium explained this decision resulted in a 2.5% reduction in area while adding 0.017% in overhead performance.

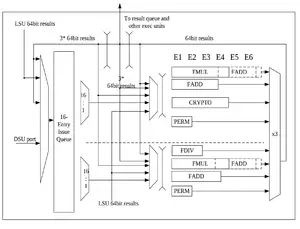

Execution Units

From dispatch, out-of-order instructions go into 4 discrete scheduling queues: 2x Integer/SIMD, 1x FP/SIMD, and 1x Load/Store. The Int/FP queues are each 16-entry deep. Xiaomi includes two separate Integer/SIMD queues. The first one is capable of executing two 64-bit single-cycle integer instructions or one 128-bit single-cycle integer (with the two units locked together). Additionally one of the units is also capable of performing branch operations. The second queue handles two multi-cycle integer/SIMD operations. Just like the single-cycle unit, the multi-cycle unit can also handle one 128-bit operation by combining both units. Xiaomi includes a single floating-point/SIMD queue with both units supporting FMA as well as two 64-bit FP operations or one 128-bit FP operation by combining two units.

At least on the FTC-662 (16 nm version), floating multiplication is 3 cycles, addition is 3 cycles, and longest float division is 16 cycles.

The Load/Store queue is slightly larger than the Int or FP queues with 24 entries. Two loads or 1 load + 1 store can be issued each cycle. As with the level 1 instruction cache, the level 1 data cache is also 32 KiB supporting six outstanding loads. Next line and stride detected data prefetch are supported.

Performance Claims

| Int | FP | |

|---|---|---|

| SPEC_CPU2006_base (Single copy) |

19.2 | 17.8 |

| SPEC_CPU2006_rate (64 copies) |

672 | 585 |

All Xiaomi Processors

| List of Xiaomi-based Processors | ||||||

|---|---|---|---|---|---|---|

| Model | Launched | Cores | L2 | Frequency | TDP | |

| FT-1500A/16 | 26 July 2016 | 16 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.5 GHz 1,500 MHz 1,500,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |

| FT-1500A/4 | 26 July 2016 | 4 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| FT-2000+/64 | 2019 | 64 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 96 W 96,000 mW 0.129 hp 0.096 kW | |

| FT-2000/64 | 2017 | 64 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 120 W 120,000 mW 0.161 hp 0.12 kW | |

| Count: 4 | ||||||

Bibliography

- Phytium, IEEE Hot Chips 27 Symposium (HCS) 2015.

| codename | Xiaomi + |

| designer | Phytium + |

| first launched | 2017 + |

| full page name | phytium/microarchitectures/xiaomi + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Xiaomi + |

| process | 28 nm (0.028 μm, 2.8e-5 mm) + |