From WikiChip

Difference between revisions of "phytium/microarchitectures/mars ii"

(→Die) |

(→Architecture) |

||

| Line 23: | Line 23: | ||

== Architecture == | == Architecture == | ||

| − | {{ | + | === Key changes from {{\\|Mars I}} === |

| + | * [[16 nm process]] (from [[28 nm]]) | ||

| + | * 15% higher frequency (2.3 GHz, up from 2 GHz) | ||

| + | * -25% lower power (96 W [[TDP]], down from 120 W) | ||

| + | * Core | ||

| + | ** FTC-662 (from FTC-661/0) | ||

| + | * System memory | ||

| + | ** [[DDR4]] (from [[DDR3]]) | ||

| + | ** Higher data rates (2666 MT/s, up from 1600 MT/s) | ||

| + | {{expand list}} | ||

== Overview == | == Overview == | ||

Revision as of 00:41, 19 February 2019

| Edit Values | |

| Mars II µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Phytium |

| Manufacturer | TSMC |

| Introduction | 2019 |

| Process | 16 nm |

| Core Configs | 64 |

| Pipeline | |

| Type | Superscalar, Pipelined |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | ARMv8 |

| Succession | |

Mars II is the successor to Mars I, an ARM server SoC microarchitecture designed by Phytium Technology for the Chinese server market.

Process technology

| This section is empty; you can help add the missing info by editing this page. |

Architecture

Key changes from Mars I

- 16 nm process (from 28 nm)

- 15% higher frequency (2.3 GHz, up from 2 GHz)

- -25% lower power (96 W TDP, down from 120 W)

- Core

- FTC-662 (from FTC-661/0)

- System memory

This list is incomplete; you can help by expanding it.

Overview

| This section is empty; you can help add the missing info by editing this page. |

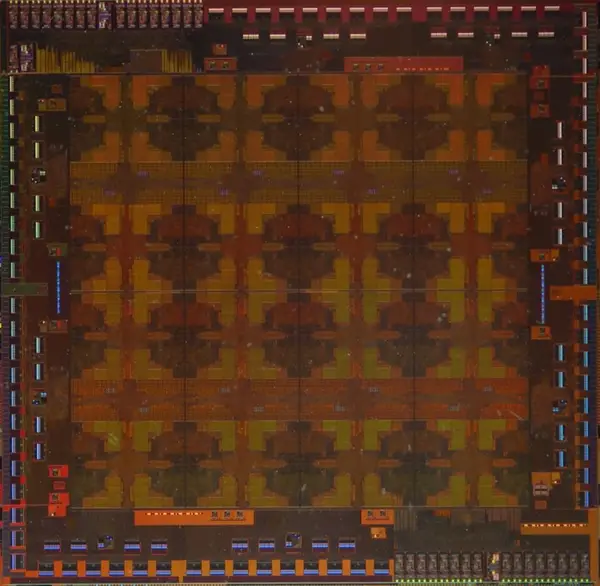

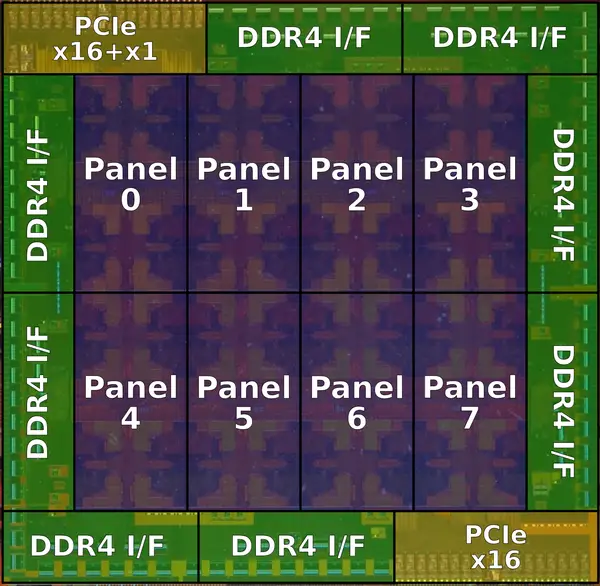

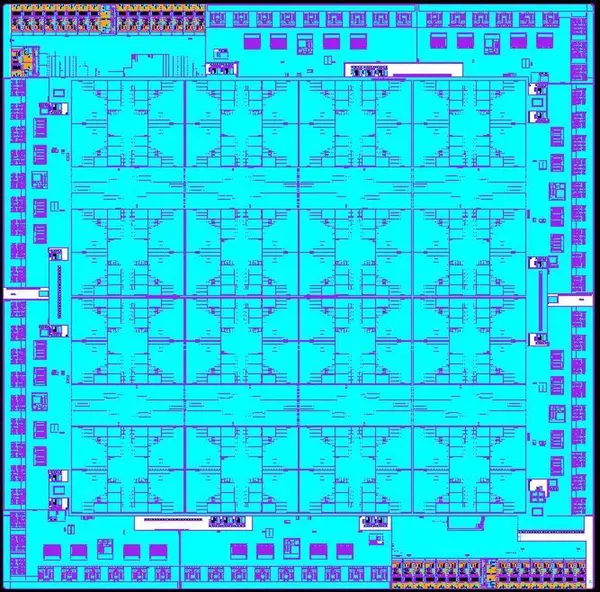

Die

- 16 nm process (16FF+) GL

- 1 Poly, 11 Metal layers, RDL

- 6,000,000,000 transistors

- 370 mm² die size

Facts about "Mars II - Microarchitectures - Phytium"

| codename | Mars II + |

| core count | 64 + |

| designer | Phytium + |

| first launched | 2019 + |

| full page name | phytium/microarchitectures/mars ii + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Mars II + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |