From WikiChip

Editing nudt/matrix-2000

Warning: You are not logged in. Your IP address will be publicly visible if you make any edits. If you log in or create an account, your edits will be attributed to your username, along with other benefits.

The edit can be undone.

Please check the comparison below to verify that this is what you want to do, and then save the changes below to finish undoing the edit.

This page supports semantic in-text annotations (e.g. "[[Is specified as::World Heritage Site]]") to build structured and queryable content provided by Semantic MediaWiki. For a comprehensive description on how to use annotations or the #ask parser function, please have a look at the getting started, in-text annotation, or inline queries help pages.

| Latest revision | Your text | ||

| Line 28: | Line 28: | ||

<blockquote>Intel was informed in August by the U.S Department of Commerce that an export license was required for the shipment of Xeon and Xeon Phi parts for use in specific previously disclosed supercomputer projects with Chinese customer INSPUR. Intel complied with the notification and applied for the license which was denied. We are in compliance with the U.S. law.</blockquote> | <blockquote>Intel was informed in August by the U.S Department of Commerce that an export license was required for the shipment of Xeon and Xeon Phi parts for use in specific previously disclosed supercomputer projects with Chinese customer INSPUR. Intel complied with the notification and applied for the license which was denied. We are in compliance with the U.S. law.</blockquote> | ||

| − | Due to the ban, NUDT was unable to obtain the Xeon Phis they' | + | Due to the ban, NUDT was unable to obtain the Xeon Phis they've hoped for in order to upgrade the system. Although the Matrix-2000 was in the planning prior to the ban, to achieve the desired upgrades without the embargoed parts, NUDT accelerated the development of the Matrix-2000 accelerators. While not nearly as powerful as {{intel|Knights Landing|l=arch}}, the chips were more powerful than the first-generate {{intel|Knights Corner|l=arch}} parts they have replaced. While the original (KL) system was planned to exceed 110 [[PFLOPS]] using the Intel parts, the Matrix-2000 managed to achieve 94.97 PFLOPS. |

== Architecture == | == Architecture == | ||

Facts about "Matrix-2000 - NUDT"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | Matrix-2000 - NUDT#package + |

| base frequency | 1,200 MHz (1.2 GHz, 1,200,000 kHz) + |

| core count | 128 + |

| designer | NUDT + |

| first announced | 2015 + |

| first launched | 2017 + |

| full page name | nudt/matrix-2000 + |

| has ecc memory support | true + |

| instance of | microprocessor + |

| ldate | 2017 + |

| main image |  + + |

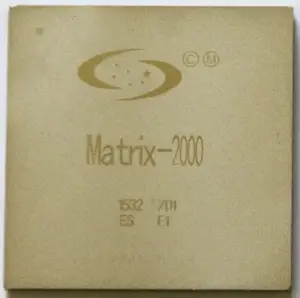

| main image caption | Matrix-2000, package front + |

| max memory bandwidth | 143.1 GiB/s (146,534.4 MiB/s, 153.652 GB/s, 153,652.455 MB/s, 0.14 TiB/s, 0.154 TB/s) + |

| max memory channels | 8 + |

| model number | Matrix-2000 + |

| name | Matrix-2000 + |

| package | FCCLGA-4201 + |

| power dissipation | 240 W (240,000 mW, 0.322 hp, 0.24 kW) + |

| supported memory type | DDR4-2400 + |

| technology | CMOS + |

| thread count | 128 + |

| word size | 64 bit (8 octets, 16 nibbles) + |