From WikiChip

Difference between revisions of "intel/process"

| Line 83: | Line 83: | ||

{{intel proc tech |year=2005 |name=P1264 |mlayers=8 |node=65 nm | {{intel proc tech |year=2005 |name=P1264 |mlayers=8 |node=65 nm | ||

|archs=Core, Modified Pentium M | |archs=Core, Modified Pentium M | ||

| − | |a1= | + | |a1=T<sub>ox</sub> |d1= |a12=Gate Dielectric |d12=SiO<sub>2</sub> |

| − | |a2= | + | |a2=V<sub>dd</sub> |d2= |a22=SRAM |d22=0.570 µm² |

| − | |a3= | + | |a3=L<sub>g</sub> |d3=35 nm |

| − | |a4= | + | |a4=CPP |d4=220 nm |a42=MMP |d42=210 nm |

}} | }} | ||

{{intel proc tech |year=2007 |name=P1266 |mlayers=9 |node=45 nm | {{intel proc tech |year=2007 |name=P1266 |mlayers=9 |node=45 nm | ||

|archs=Penryn, Nehalem | |archs=Penryn, Nehalem | ||

| − | |a1= | + | |a1=T<sub>ox</sub> |d1= |a12=Gate Dielectric |d12=High-κ |

| − | |a2= | + | |a2=V<sub>dd</sub> |d2= |a22=SRAM |d22=0.346 µm² |

| − | |a3= | + | |a3=L<sub>g</sub> |d3=25 nm |

| − | |a4= | + | |a4=CPP |d4=160 nm |a42=MMP |d42=180 nm |

}} | }} | ||

{{intel proc tech |year=2009 |name=P1268 |mlayers=10 |node=32 nm | {{intel proc tech |year=2009 |name=P1268 |mlayers=10 |node=32 nm | ||

|archs=Westmere, Sandy Bridge | |archs=Westmere, Sandy Bridge | ||

|a1=T<sub>ox</sub> |d1= |a12=Gate Dielectric |d12=High-κ | |a1=T<sub>ox</sub> |d1= |a12=Gate Dielectric |d12=High-κ | ||

| − | |a2=V<sub>dd</sub> |d2= |a22=SRAM |d22=0. | + | |a2=V<sub>dd</sub> |d2= |a22=SRAM |d22=0.148 µm² |

|a3=L<sub>g</sub> |d3=30 nm | |a3=L<sub>g</sub> |d3=30 nm | ||

|a4=CPP |d4=112.5 nm |a42=MMP |d42=112.5 nm | |a4=CPP |d4=112.5 nm |a42=MMP |d42=112.5 nm | ||

Revision as of 05:46, 11 May 2017

This article details Intel's Semiconductor Process Technology.

Timeline

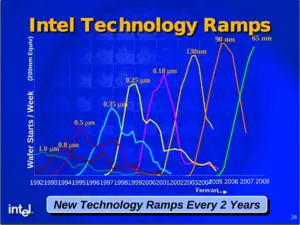

| Year | Process | Node | MLayers | µarchs | Transistor | Attributes | ||||

|---|---|---|---|---|---|---|---|---|---|---|

| CHMOS I | 3 µm | 1 | Tox | 70 nm | Gate Dielectric | |||||

| Vdd | 5 V | SRAM | 1120 µm² | |||||||

| Lg | 3.0 µm | |||||||||

| CPP | 7 µm | MMP | 11 µm | |||||||

| CHMOS II | 2 µm | 1 | Tox | 40 nm | Gate Dielectric | |||||

| Vdd | 5 V | SRAM (HD) | 1740 µm² | |||||||

| Lg | 2.0 µm | |||||||||

| CPP | 5.6 µm | MMP | 8 µm | |||||||

| 1982 | P646 (CHMOS III) | 1.5 µm | 1 | 80286, 80386 |

Tox | 25 nm | Gate Dielectric | Si2N2O | ||

| Vdd | 5 V | SRAM (HD) | 951.7 µm² | |||||||

| Lg | 1.5 µm | |||||||||

| CPP | 4.0 µm | MMP | 6.4 µm | |||||||

| 1987 | P648 | 1.0 µm | 2 | 80486 | Lg | 1,000 nm | ||||

| Tox | ? nm | Gate Dielectric | ||||||||

| Vdd | ? V | |||||||||

| 1989 | P650 | 0.8 µm | 3 | 80486 | Lg | 800 nm | ||||

| Tox | ? nm | Gate Dielectric | ||||||||

| Vdd | ? V | |||||||||

| 1993 | P852 | 0.5 µm | 4 | P5 | Lg | 500 nm | ||||

| Tox | 8.0 nm | Gate Dielectric | ||||||||

| Vdd | 3.3 V | |||||||||

| 1995 | P854 | 0.35 µm | 4 | P6 | Lg | 350 nm | ||||

| Tox | 5.2 nm | Gate Dielectric | ||||||||

| Vdd | 2.5 V | |||||||||

| 1997 | P856 P856.5 |

0.25 µm | 5 | P6 | Lg | 200 nm | ||||

| Tox | 3.1 nm | Gate Dielectric | SiO2 | |||||||

| Vdd | 1.8 V | |||||||||

| 1999 | P858 | 0.18 µm | 6 | NetBurst | Lg | 130 nm | ||||

| Tox | 2.0 nm | Gate Dielectric | SiO2 | |||||||

| Vdd | 1.6 V | |||||||||

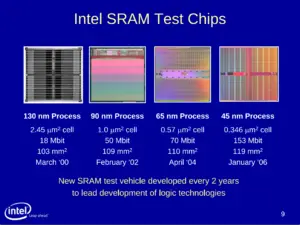

| 2001 | P860 | 0.13 µm | 6 | Pentium M | Lg | 70 nm | ||||

| Tox | 1.4 nm | Gate Dielectric | SiO2 | |||||||

| Vdd | 1.4 V | |||||||||

| SRAM (HD) | 2.45 µm² | |||||||||

| 2003 | P1262 | 90 nm | 7 | Pentium M |  |

Lg | 50 nm | |||

| Tox | 1.2 nm | Gate Dielectric | SiO2 | |||||||

| Vdd | 1.2 V | |||||||||

| SRAM (HD) | 1.00 µm² | |||||||||

| 2005 | P1264 | 65 nm | 8 | Core, Modified Pentium M |

Tox | Gate Dielectric | SiO2 | |||

| Vdd | SRAM | 0.570 µm² | ||||||||

| Lg | 35 nm | |||||||||

| CPP | 220 nm | MMP | 210 nm | |||||||

| 2007 | P1266 | 45 nm | 9 | Penryn, Nehalem |

Tox | Gate Dielectric | High-κ | |||

| Vdd | SRAM | 0.346 µm² | ||||||||

| Lg | 25 nm | |||||||||

| CPP | 160 nm | MMP | 180 nm | |||||||

| 2009 | P1268 | 32 nm | 10 | Westmere, Sandy Bridge |

Tox | Gate Dielectric | High-κ | |||

| Vdd | SRAM | 0.148 µm² | ||||||||

| Lg | 30 nm | |||||||||

| CPP | 112.5 nm | MMP | 112.5 nm | |||||||

| 2011 | P1270 | 22 nm | 11 | Ivy Bridge, Haswell |

Tox | Gate Dielectric | High-κ | |||

| Vdd | SRAM | 0.092 µm² | ||||||||

| Lg | 26 nm | |||||||||

| CPP | 90 nm | MMP | 80 nm | |||||||

| 2014 | P1272 | 14 nm | 11 | Broadwell, Skylake, Kaby Lake, Coffee Lake |

Tox | Gate Dielectric | High-κ | |||

| Vdd | SRAM | 0.0499 µm² | ||||||||

| Lg | 20 nm | |||||||||

| CPP | 70 nm | MMP | 52 nm | |||||||

| 2017 | P1274 | 10 nm | Cannonlake, Icelake, Tigerlake |

Tox | Gate Dielectric | High-κ | ||||

| Vdd | SRAM | 0.0312 µm² | ||||||||

| Lg | 18 nm ? | |||||||||

| CPP | 54 nm | MMP | 36 nm | |||||||

| 2019 | P1276 | 7 nm | ||||||||

| 2022 | P1278 | 5 nm | ||||||||