(basic info) |

|||

| Line 64: | Line 64: | ||

|successor link=intel/microarchitectures/willow cove | |successor link=intel/microarchitectures/willow cove | ||

}} | }} | ||

| − | '''Sunny Cove''' is the successor to {{\\|Palm Cove}}, a high-performance [[10 nm]] [[x86]] core microarchitecture designed by [[Intel]] for an array of server and client products. | + | '''Sunny Cove''' is the successor to {{\\|Palm Cove}}, a high-performance [[10 nm]] [[x86]] core microarchitecture designed by [[Intel]] for an array of server and client products, including {{\\|Ice Lake (Client)}}, {{\\|Ice Lake (Server)}}, {{\\|Lakefield}}, and the Nervana {{nervana|NNP-I}}. |

== History == | == History == | ||

Revision as of 22:57, 18 May 2019

| Edit Values | |

| Sunny Cove µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2019 |

| Process | 10 nm |

| Core Configs | 2, 4 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 14-19 |

| Instructions | |

| ISA | x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AVX, AVX2, AES, PCLMUL, FSGSBASE, RDRND, FMA3, F16C, BMI, BMI2, VT-x, VT-d, TXT, TSX, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVE, SGX, MPX, AVX-512 |

| Cache | |

| L1I Cache | 32 KiB/core 8-way set associative |

| L1D Cache | 48 KiB/core 12-way set associative |

| L2 Cache | 512 MiB/core 8-way set associative |

| L3 Cache | 2 MiB/core 16-way set associative |

| Succession | |

Sunny Cove is the successor to Palm Cove, a high-performance 10 nm x86 core microarchitecture designed by Intel for an array of server and client products, including Ice Lake (Client), Ice Lake (Server), Lakefield, and the Nervana NNP-I.

Contents

History

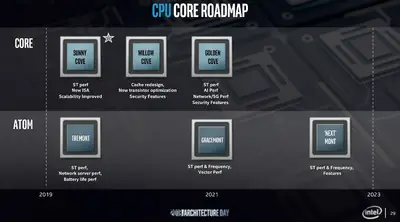

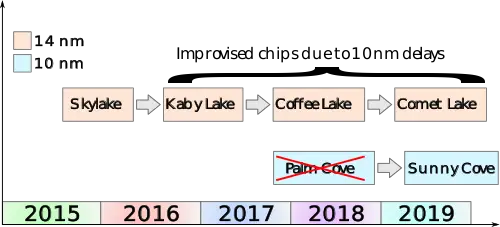

Sunny Cove was originally unveiled by Intel at their 2018 architecture day. Intel originally intended for Sunny Cove to succeed Palm Cove in late 2017 which was it was intended to be the first 10 nm-based core and the proper successor to Skylake. Prolong delays and problems with their 10 nm process and resulted in a number of improvised derivatives of Skylake including Kaby Lake, Coffee Lake, and Comet Lake. For all practical purposes, Palm Cove has been skipped and Intel has gone directly to Sunny Cove. Sunny Cove is expected to debut in mid-2019.

Process Technology

Sunny Cove is designed to take advantage of Intel's 10 nm process.

Architecture

Key changes from Palm Cove

This list is incomplete; you can help by expanding it.

New instructions

Sunny Cove introduced a number of new instructions:

-

CLWB- Force cache line write-back without flush -

RDPID- Read Processor ID - Additional AVX-512 extensions:

-

AVX512VPOPCNTDQ- AVX-512 Vector Population Count Doubleword and Quadword -

AVX512VNNI- AVX-512 Vector Neural Network Instructions -

AVX512GFNI- AVX-512 Galois Field New Instructions -

AVX512VAES- AVX-512 Vector AES -

AVX512VBMI2- AVX-512 Vector Bit Manipulation, Version 2 -

AVX512BITALG- AVX-512 Bit Algorithms -

AVX512VPCLMULQDQ- AVX-512 Vector Vector Carry-less Multiply

-

-

SSE_GFNI- SSE-based Galois Field New Instructions -

AVX_GFNI- AVX-based Galois Field New Instructions - Split Lock Detection - detection and cause an exception for split locks

- Fast Short REP MOV

Overview

Sunny Cove is Intel's core microarchitecture for a series of client and server chips that succeed Palm Cove (and effectively the Skylake series of derivative). Sunny cove introduces a very large set of enhancements and improvements of its predecessor including a wider and deeper pipeline. Sunny Cove is implemented in a number of chips including Lakefield, Ice Lake (Client), and Ice Lake (Server).

Die

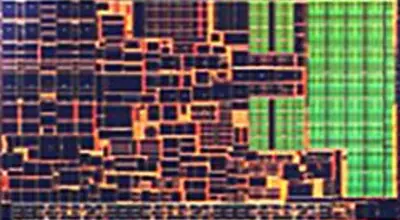

Core

- 10nm+ process

- Core from an Ice Lake SoC

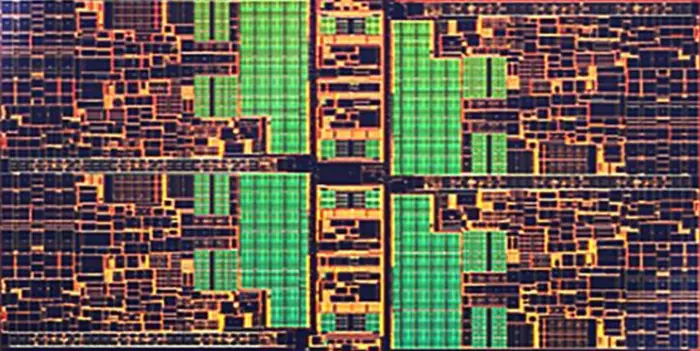

Core group

- 10nm+ process

- Quad-core from an Ice Lake SoC

Bibliography

- Intel Architecture Day 2018, December 11, 2018

| codename | Sunny Cove + |

| core count | 2 + and 4 + |

| designer | Intel + |

| first launched | 2019 + |

| full page name | intel/microarchitectures/sunny cove + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Sunny Cove + |

| pipeline stages (max) | 19 + |

| pipeline stages (min) | 14 + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |