From WikiChip

Editing intel/loihi

Warning: You are not logged in. Your IP address will be publicly visible if you make any edits. If you log in or create an account, your edits will be attributed to your username, along with other benefits.

The edit can be undone.

Please check the comparison below to verify that this is what you want to do, and then save the changes below to finish undoing the edit.

This page supports semantic in-text annotations (e.g. "[[Is specified as::World Heritage Site]]") to build structured and queryable content provided by Semantic MediaWiki. For a comprehensive description on how to use annotations or the #ask parser function, please have a look at the getting started, in-text annotation, or inline queries help pages.

| Latest revision | Your text | ||

| Line 37: | Line 37: | ||

== Architecture == | == Architecture == | ||

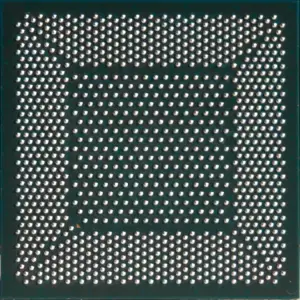

[[File:loihi mesh chips.png|right|300px]] | [[File:loihi mesh chips.png|right|300px]] | ||

| − | The chip consists of a [[many-core]] mesh of 128 neuromorphic cores, three {{intel|Lakemont|l=arch|Lakemont}} | + | The chip consists of a [[many-core]] mesh of 128 neuromorphic cores, three {{intel|Lakemont|l=arch|Lakemont x86 cores}} ({{intel|Quark}}), and an off-chip communication interface that allows the chip to scale out to many other chips in the four planar directions (as shown on the right). The implemented mesh protocol supports up to 4,096 on-chip cores and up to 16,384 chips. |

The chip itself implements a fully asynchronous [[many-core]] [[mesh topology|mesh]] of 128 neuromorphic cores. It implements a [[spiking neural network]] (SNN) whereby at any given time one or more of the implemented neurons may send out an impulse (i.e., spike) to its neighbors through the directed links (synapses). All neurons have a local state with their own set of rules that affects their evolution and the timing of spike generation. Interaction is entirely asynchronous, sporadic, and independent of any other neuron on the network. A unique feature of Loihi's neuromorphic cores is their integrated learning engine which enables full on-chip learning via programmable microcode learning rules. | The chip itself implements a fully asynchronous [[many-core]] [[mesh topology|mesh]] of 128 neuromorphic cores. It implements a [[spiking neural network]] (SNN) whereby at any given time one or more of the implemented neurons may send out an impulse (i.e., spike) to its neighbors through the directed links (synapses). All neurons have a local state with their own set of rules that affects their evolution and the timing of spike generation. Interaction is entirely asynchronous, sporadic, and independent of any other neuron on the network. A unique feature of Loihi's neuromorphic cores is their integrated learning engine which enables full on-chip learning via programmable microcode learning rules. | ||

Facts about "Loihi - Intel"

| back image |  + + |

| core voltage (max) | 1.25 V (12.5 dV, 125 cV, 1,250 mV) + |

| core voltage (min) | 0.5 V (5 dV, 50 cV, 500 mV) + |

| designer | Intel + |

| die area | 60 mm² (0.093 in², 0.6 cm², 60,000,000 µm²) + |

| first announced | September 25, 2017 + |

| first launched | January 2018 + |

| full page name | intel/loihi + |

| instance of | neuromorphic chip + |

| ldate | January 2018 + |

| main image |  + + |

| manufacturer | Intel + |

| market segment | Artificial Intelligence + |

| max cpu count | 16,384 + |

| name | Loihi + |

| neuron count | 131,072 + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| smp max ways | 16,384 + |

| synapse count | 130,000,000 + |

| technology | CMOS + |

| transistor count | 2,070,000,000 + |