From WikiChip

Editing greenwaves/gap8

Warning: You are not logged in. Your IP address will be publicly visible if you make any edits. If you log in or create an account, your edits will be attributed to your username, along with other benefits.

The edit can be undone.

Please check the comparison below to verify that this is what you want to do, and then save the changes below to finish undoing the edit.

This page supports semantic in-text annotations (e.g. "[[Is specified as::World Heritage Site]]") to build structured and queryable content provided by Semantic MediaWiki. For a comprehensive description on how to use annotations or the #ask parser function, please have a look at the getting started, in-text annotation, or inline queries help pages.

| Latest revision | Your text | ||

| Line 37: | Line 37: | ||

The microcontroller block is a fairly standard MCU with many of the standard features. The MCU is situated on its own power domain with the peripherals power switchable and configurable along with the clock generator. It consists of a single system management core (also called a fabric controller by GreenWaves) for tasks such as peripherals and it can double as general purpose low-power core, meaning compute engine can remain power-gated unless absolutely necessary. This core has its own 16 KiB of data cache and 4 KiB of instruction cache. | The microcontroller block is a fairly standard MCU with many of the standard features. The MCU is situated on its own power domain with the peripherals power switchable and configurable along with the clock generator. It consists of a single system management core (also called a fabric controller by GreenWaves) for tasks such as peripherals and it can double as general purpose low-power core, meaning compute engine can remain power-gated unless absolutely necessary. This core has its own 16 KiB of data cache and 4 KiB of instruction cache. | ||

| − | The chip features [[nine cores]] (1 serving in the MCU + 8 in the compute engine), all are fully compliant {{arch|32}} [[RISC-V]] cores with support for the {{risc-v|m|integer multiplication and division instructions}} (M) and {{risc-v|c|compressed instructions}} (C) {{risc-v|standard extensions}} (i.e., | + | The chip features [[nine cores]] (1 serving in the MCU + 8 in the compute engine), all are fully compliant {{arch|32}} [[RISC-V]] cores with support for the {{risc-v|m|integer multiplication and division instructions}} (M) and {{risc-v|c|compressed instructions}} (C) {{risc-v|standard extensions}} (i.e., RVIMC). |

The MCU was designed to feel and behave like any other microcontroller on the market. It can be programmed using the familiar standard GCC/GDB toolchain derived from the one developed by the RISC-V foundation. Currently two real-time operating systems are supported, the PULP OS and Arm Mbed OS. GreenWaves has developed a full set of drivers for both of those operating systems in order to allow access to all the GAP8 peripherals. | The MCU was designed to feel and behave like any other microcontroller on the market. It can be programmed using the familiar standard GCC/GDB toolchain derived from the one developed by the RISC-V foundation. Currently two real-time operating systems are supported, the PULP OS and Arm Mbed OS. GreenWaves has developed a full set of drivers for both of those operating systems in order to allow access to all the GAP8 peripherals. | ||

Facts about "GAP8 - GreenWaves"

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | GAP8 - GreenWaves#package + |

| base frequency | 250 MHz (0.25 GHz, 250,000 kHz) + |

| core count | 9 + |

| core voltage (max) | 1.2 V (12 dV, 120 cV, 1,200 mV) + |

| core voltage (min) | 1 V (10 dV, 100 cV, 1,000 mV) + |

| designer | GreenWaves + |

| first announced | October 2016 + |

| first launched | February 26, 2018 + |

| full page name | greenwaves/gap8 + |

| instance of | microprocessor + |

| io voltage | 1.8 V (18 dV, 180 cV, 1,800 mV) + and 3.3 V (33 dV, 330 cV, 3,300 mV) + |

| isa | RV32IMC + |

| isa family | RISC-V + |

| l1$ size | 100 KiB (102,400 B, 0.0977 MiB) + |

| l1d$ size | 80 KiB (81,920 B, 0.0781 MiB) + |

| l1i$ size | 20 KiB (20,480 B, 0.0195 MiB) + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | February 26, 2018 + |

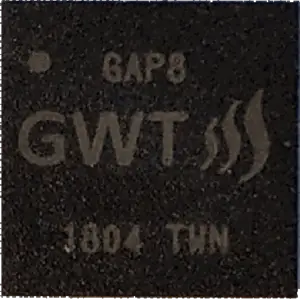

| main image |  + + |

| main image caption | GAP8, front package + |

| manufacturer | TSMC + |

| market segment | Embedded + |

| max cpu count | 1 + |

| model number | GAP8 + |

| name | GAP8 + |

| package | aQFN + |

| power dissipation | 0.06 W (60 mW, 8.046e-5 hp, 6.0e-5 kW) + |

| process | 55 nm (0.055 μm, 5.5e-5 mm) + |

| release price | $ 5.00 (€ 4.50, £ 4.05, ¥ 516.65) + |

| smp max ways | 1 + |

| technology | CMOS + |

| thread count | 9 + |

| word size | 32 bit (4 octets, 8 nibbles) + |