-

WikiChip

WikiChip

-

Architectures

Popular x86

-

Intel

- Client

- Server

- Big Cores

- Small Cores

-

AMD

Popular ARM

-

ARM

- Server

- Big

- Little

-

Cavium

-

Samsung

-

-

Chips

Popular Families

-

Ampere

-

Apple

-

Cavium

-

HiSilicon

-

MediaTek

-

NXP

-

Qualcomm

-

Renesas

-

Samsung

-

From WikiChip

Cache Coherent Interconnect for Accelerators (CCIX)

| v · d · e | |

| Interconnect Architectures | |

| |

| Concepts | |

| General | |

| Peripheral | |

| Storage Devices | |

| Audio Devices | |

Cache Coherent Interconnect for Accelerators (CCIX), pronounced "see-six", is an open cache coherent interconnect architecture developed by the CCIX Consortium.

Overview

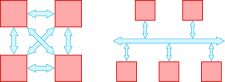

CCIX is a high-performance, low latency, chip-to-chip interconnect architecture that provides a cache coherent framework for heterogeneous system architectures. Cache coherency is automatically maintained at all time between the central processing unit and the various other accelerators in the system. CCIX supports signaling rates between 16 GT/s and 25 GT/s per link with support for link aggregation for higher performance.

Retrieved from "https://en.wikichip.org/w/index.php?title=ccix&oldid=81017"