(→Basic design) |

|||

| Line 3: | Line 3: | ||

== Basic design == | == Basic design == | ||

<div style="float:right;"> | <div style="float:right;"> | ||

| − | <math>A + B = Q | + | <math> |

| − | + | A + B = Q \\ | |

| − | + | 0_2 + 0_2 = 00_2 \\ | |

| − | + | 0_2 + 1_2 = 01_2 \\ | |

| − | + | 1_2 + 0_2 = 01_2 \\ | |

| + | 1_2 + 1_2 = 10_2 | ||

| + | </math> | ||

</div> | </div> | ||

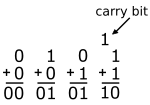

A 1-bit adder adds two single-bit values together. There are four such possible operations. All but the 1+1 operation result in a single-digit sum. The 1+1 operation produces a sum with two digits. The higher significant bit of that value is known as a carry. The digital component that performs the addition of two bits is called a '''half adder'''. When two multi-bit numbers are added together, the carry out from the lower bit must be accounted for in the higher addition of the higher bits. When a half adder accounts for a carry in, it becomes a '''full adder'''. | A 1-bit adder adds two single-bit values together. There are four such possible operations. All but the 1+1 operation result in a single-digit sum. The 1+1 operation produces a sum with two digits. The higher significant bit of that value is known as a carry. The digital component that performs the addition of two bits is called a '''half adder'''. When two multi-bit numbers are added together, the carry out from the lower bit must be accounted for in the higher addition of the higher bits. When a half adder accounts for a carry in, it becomes a '''full adder'''. | ||

| − | == Half Adders (HA) == | + | === Half Adders (HA) === |

| − | {{ | + | {{main|Half adder}} |

| + | |||

| + | {| class="wikitable left" style="float:left; margin: 15px;" | ||

| + | !colspan="5"|Half Adder | ||

| + | |- | ||

| + | !colspan="2"|Input!!C<sub>out</sub>!!S!!Q<sub>10</sub> | ||

| + | |- | ||

| + | |0||0||0||0||0 | ||

| + | |- | ||

| + | |0||1||0||1||1 | ||

| + | |- | ||

| + | |1||0||0||1||1 | ||

| + | |- | ||

| + | |1||1||1||0||2 | ||

| + | |} | ||

| + | [[File:1-bit addition.svg|right|150px]] | ||

| + | A '''half adder''' is a simple device that adds two single bit inputs. The result of a half adder (in base 10) is either 0, 1, or 2. Two bits are required to represent that output; they are called the '''sum''' S and '''carry-out''' C<sub>out</sub>. The carry-out of one half adder is typically used as the carry-in of the next half adder. For that reason it is said to have double the weight of the other bit. | ||

| + | |||

| + | The sum is 1 only when one of the operands is 1, otherwise it's 0. This can be realized by simply [[XORing]] them together. The carry out bit is one only when both addends are one; [[ANDing]] the two bits will generate the desired output. | ||

| + | |||

| + | <math> | ||

| + | S = A \oplus B \\ | ||

| + | C_{out} = A \cdot B | ||

| + | </math> | ||

| + | |||

| + | {{clear}} | ||

| + | === Full Adder (FA) === | ||

| + | {{main|full adder}} | ||

| + | |||

| + | [[File:Full adder black box.svg|right|150px]] | ||

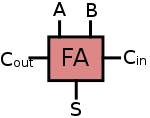

| + | A major drawback of a half adder is that it lacks the ability to add two bits and account for a carry-in that might have been brought from the previous digit. As previously stated, the carry-out of one half adder is the carry-in of the next half adder. A '''full adder''' is a simple device that can receive a carry-in bit input in addition to adding two single bit inputs. A full adder has three inputs A, B, and C<sub>in</sub> and two outputs S and C<sub>out</sub>. Full adders are typically combined together in a cascading way (C<sub>in</sub> to <sub>out</sub>), creating ''N''-bit adders (16, 32, 64, etc..). | ||

| + | |||

| + | The sum output can be expressed as: | ||

| − | == | + | <math> |

| − | + | S = A \oplus B \oplus C \\ | |

| + | C_{out} = \text{Majority}(A, B, C) | ||

| + | </math> | ||

== BCD Adders == | == BCD Adders == | ||

| Line 23: | Line 59: | ||

== Advanced Designs == | == Advanced Designs == | ||

| + | {{empty section}} | ||

| + | |||

| + | === PGK Cell === | ||

{{empty section}} | {{empty section}} | ||

[[Category:Adders]] | [[Category:Adders]] | ||

Revision as of 19:01, 12 April 2014

An adder (sometimes called a summer) is a digital circuit that adds two N-bit numbers and generates an N-bit number. In addition to generating a sum, adders often also generate an overflow flag and a carry flag. Adders are used in many parts of the microprocessor such as the ALU, PC, counters, calculating effective addresses and table indices, multipliers, filters, and in various other components.

Contents

Basic design

A 1-bit adder adds two single-bit values together. There are four such possible operations. All but the 1+1 operation result in a single-digit sum. The 1+1 operation produces a sum with two digits. The higher significant bit of that value is known as a carry. The digital component that performs the addition of two bits is called a half adder. When two multi-bit numbers are added together, the carry out from the lower bit must be accounted for in the higher addition of the higher bits. When a half adder accounts for a carry in, it becomes a full adder.

Half Adders (HA)

- Main article: Half adder

| Half Adder | ||||

|---|---|---|---|---|

| Input | Cout | S | Q10 | |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 2 |

A half adder is a simple device that adds two single bit inputs. The result of a half adder (in base 10) is either 0, 1, or 2. Two bits are required to represent that output; they are called the sum S and carry-out Cout. The carry-out of one half adder is typically used as the carry-in of the next half adder. For that reason it is said to have double the weight of the other bit.

The sum is 1 only when one of the operands is 1, otherwise it's 0. This can be realized by simply XORing them together. The carry out bit is one only when both addends are one; ANDing the two bits will generate the desired output.

Full Adder (FA)

- Main article: full adder

A major drawback of a half adder is that it lacks the ability to add two bits and account for a carry-in that might have been brought from the previous digit. As previously stated, the carry-out of one half adder is the carry-in of the next half adder. A full adder is a simple device that can receive a carry-in bit input in addition to adding two single bit inputs. A full adder has three inputs A, B, and Cin and two outputs S and Cout. Full adders are typically combined together in a cascading way (Cin to out), creating N-bit adders (16, 32, 64, etc..).

The sum output can be expressed as:

BCD Adders

- Main article: BCD Adder

Most adders typically use the binary numeral system, however they can use any other numerical representation such as binary-coded decimal. Binary adders are typically simpler to design when compared to a BCD adder where roughly 20 percent more circuitry is required.

Advanced Designs

| This section is empty; you can help add the missing info by editing this page. |

PGK Cell

| This section is empty; you can help add the missing info by editing this page. |