6932852 PANASONIC INDL. ELECTRONIC マイクロコンピュータ(4-Bit)

72C 05681 D7-49-04

MN1400 Family

## MN1400 Family

## 4 ビット・1 チップ・マイクロコンピュータ 4-Bit Single-Chip Microcomputers

#### ■ MN1400 ファミリ製品系列/Series in MN1400 Family

| MN1400     | 分 類                            | シリーズ名   | プロセス    | 機能・用途                     | Function · Use      |  |

|------------|--------------------------------|---------|---------|---------------------------|---------------------|--|

| Family No. | Category                       | Series  | Process |                           |                     |  |

|            | 汎 用<br>General Purpose         | MN1400  | NMOS    |                           |                     |  |

| 3          |                                | MN1430  | PMOS    | 汎用タイプ                     | General Purpose     |  |

|            |                                | MN1450  | CMOS    |                           |                     |  |

| 1          |                                | MN1420  | NMOS    | LED 駆動タイプ                 | LED Driver Type     |  |

|            |                                | MN1460  |         | 低電圧タイプ                    | Low Voltage Type    |  |

|            |                                | MN1456A | смоѕ    | デュアルタイプ                   | Dual Type           |  |

|            |                                | MN14531 | [       | 家電用複合タイプ                  | For House Appliance |  |

|            | <b>蛍光表示管駆動用</b>                | MN1450B | CMOS    | 高耐圧タイプ                    | High Voltage Type   |  |

| 2          | FLT Driver                     |         |         | 一                         |                     |  |

|            | TV 電子選局用                       | MN1410  | NMOS    | テレビ,ビデオチューナ用              | For TV, VTR Tuner   |  |

| 3          | TV Electronic<br>Tuning System | MN1480  | CMOS    | / / / C, C / / / X - / // | 101 11, 111 14101   |  |

|            | ラジオ電子チューナ用                     | MAN 407 | CMOS    | オーディオチューナ用                | For Audio Tuner     |  |

| 4          | Radio Synthesizer Tuner        | MN1427  | CMOS    | オー/イオ/エ・/用                |                     |  |

#### ■ 概 要

MN1400 ファミリは、4 ビット並列 ALU, ROM, RAM, I/O ポートなどを 1 チップに集積した 4 ビット・1 チップ・マイクロコンピュータのファミリで、NMOS、PMOS、CMOS 標準タイプ、低電圧タイプ、電子選局専用タイプなど、豊富な品種レンジが準備されており、各種の制御に最適なマイクロコンピュータを選択できます。

#### **■** Description

The MN1400 family are 4-bit single-chip microcomputers with a 4-bit ALU, a ROM, a RAM, I/O ports, etc. on a single semiconductor chip. Various versions of microcomputers including NMOS, PMOS and CMOS standard versions, and dedicated versions for tuning systems are supported, making the MN1400 family suitable for a wide variety of control functions.

#### ■特徴

- 品種レンジが豊富で、最適なマイクロコンピュータの 選択が可能

- Nチャンネルタイプは,LOCOS E/D MOS で高速

- Pチャンネルタイプは、LOCOS E/D MOS で高電圧

- ●CMOSタイプは、CMOS LOCOSで低消費電力

- ●単一 + 5 V (N チャンネル, CMOS タイプ), -15 V (Pチャンネルタイプ)電源動作で、あらゆる機器への応用に有利

- ●動作温度範囲が広い:-30~+70°C

- Nチャンネル, CMOS タイプは, TTL/CMOS コンパ チブル

- Pチャンネルタイプは、蛍光表示管直接駆動

- ●強力な入出力機能

- プログラマブル 8 ビットカウンタ内蔵

- ●標準75種類の使いやすい豊富なインストラクション

## PANASONIC INDL/ELEK {IC} 72 DE 6932852 0005682 3

### 6932852 PANASONIC INDL. ELECTRONIC マイクロコンピュータ(4-Bit)

DT-49-19-04 72C 05682 MN1400 Family

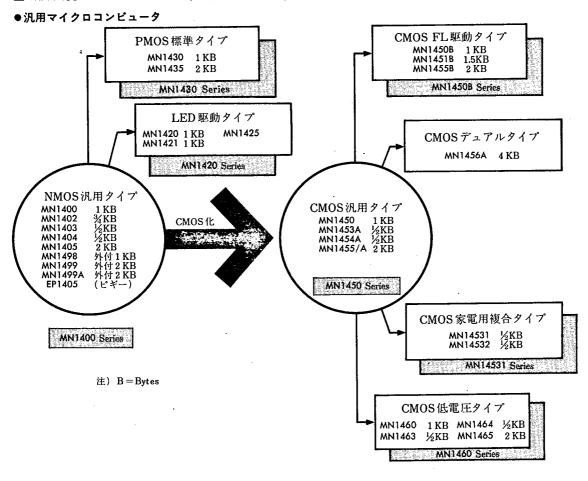

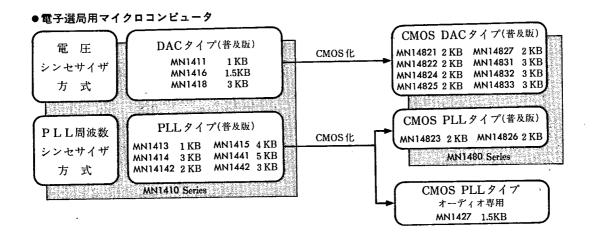

■ MN 1400ファミリ製品展開図/MN 1400 Family Products Map

6932852 PANASONIC INDL. ELECTRONIC マイクロコンピュータ(4-Bit)

72C 05683 D 7-49-19-04 MN1400 Family

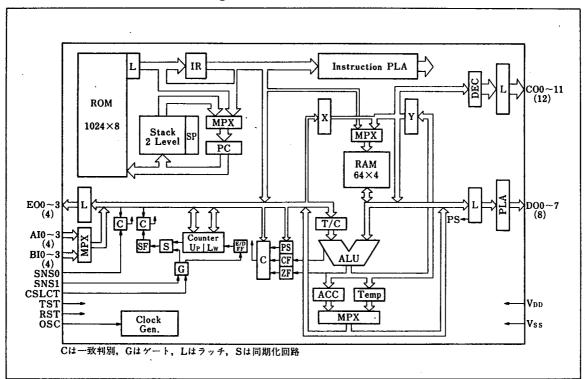

#### ■ 基本ブロック図/Basic Block Diagram

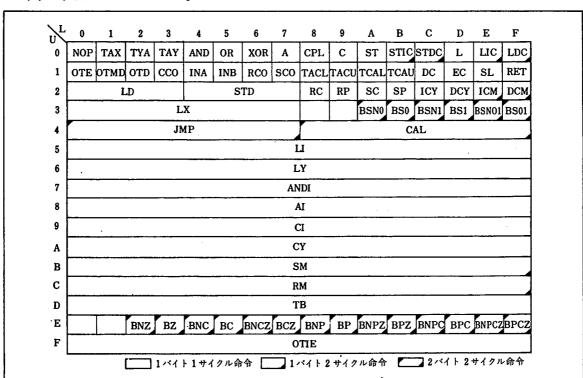

#### ■ 命令マップ/Instruction Map

6932852 PANASONIC INDL. ELECTRONIC 72C 05684 D7-49-19-04 マイクロコンピュータ(4-Bit)

MN1400 Family

#### ■ 機能説明

| 記 号                              | ブロック名         | 機能説明                                                                                                |  |  |  |  |  |  |  |  |

|----------------------------------|---------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| ALU                              | 演算論理ユニット      | データの各種処理判定を行なう回路。<br>動作モードには、AND (論理積)、OR (論理和)、<br>Exclusive OR (排他的論理和)、および ADD (加算)<br>の4モードがある。 |  |  |  |  |  |  |  |  |

| ACC                              | アキュムレータ       | 演算装置にある主要な4ビットのレジスタで,動作中に処理されるほとんどのデータを扱う。                                                          |  |  |  |  |  |  |  |  |

| ТЕМР                             | テンポラリレジスタ     | レジスタの一種で、アキュムレータの内容を保存する必要<br>のある場合に利用される。                                                          |  |  |  |  |  |  |  |  |

| PS                               | プログラムステータス    | プログラム中、任意に用いることができるフラグで、命令<br>SP、RPによってセット、リセットされる。<br>フラグは、システムの状態を記憶する1ビットのフリップ<br>フロップ。          |  |  |  |  |  |  |  |  |

| CF                               | キャリフラグ        | データを ALU で処理した結果、最上位ビットからの桁上<br>げが生じたときにセットされるフラグ。<br>命令 SC、RC によってもセット、リセットされる。                    |  |  |  |  |  |  |  |  |

| ZF                               | ゼロフラグ         | データ処理の結果がゼロの場合セットされるフラグ。                                                                            |  |  |  |  |  |  |  |  |

| RAM                              | ランダムアクセス・メモリ  | システムの制御に必要なデータを記憶する書込み、読出し可能なメモリ。<br>MN1400 には 1 語 4 ビットで 64 語用意され、X レジスタと Y レジスタでアドレスを指定。          |  |  |  |  |  |  |  |  |

| х                                | X レジスタ        | RAM の1語 M (X, Y) のアドレスを指定する X の 値を<br>保持する 3 ビットのレジスタ。                                              |  |  |  |  |  |  |  |  |

| Y                                | Y レジスタ        | RAM の1語 M (X, Y) のアドレスを指定する Y の値を保持する 4 ビットのレジスタ。<br>Y レジスタは、RAM のアドレス指定以外に C 出力ポートの端子も指定。          |  |  |  |  |  |  |  |  |

| PC                               | プログラムカウンタ     | 11 ビットのバイナリカウンタで、命令記憶用の ROM を最大 2048 ワード指定可能。                                                       |  |  |  |  |  |  |  |  |

| STACK                            | スタック          | サブルーチン実行時にプログラムカウンタの内容を退避させるためのレジスタで2 レベル各 11 ビットある。                                                |  |  |  |  |  |  |  |  |

| ROM                              | リードオンリ・メモリ    | 命令を記憶し読出し専用に使用されるメモリ。<br>MN1400 には 1 ワード 8 ビット構成で 1024 ワード用意 されている。                                 |  |  |  |  |  |  |  |  |

| IR                               | インストラクションレジスタ | ROM から読み出された命令を命令実行サイクルの間ラッチする8ピットのレジスタ。                                                            |  |  |  |  |  |  |  |  |

| INSTRUCTION インストラクション PLA<br>PLA |               | 命令語をデコードする AND 部と OR 部とからなる PLA                                                                     |  |  |  |  |  |  |  |  |

| COUNTR                           | カウンタ          | クロックバルスとは関係なく外部からの信号によってカウントする上下各4ビット計8ビットのパイナリ・リブルスウンタ。                                            |  |  |  |  |  |  |  |  |

## 6932852 PANASONIC INDL. ELECTRONIC 72C 05685 D 7-49-/9-04 マイクロコンピュータ(4-Bit)

MN1400 Family

| 記号        | ブロック名                          | 機能説明                                                                                                                           |  |  |  |  |  |  |

|-----------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| L         | ラッチ                            | データ処理回路とデータ入出力および表示部などの間でデータを保持。<br>出力ポートは、すべてラッチ付。                                                                            |  |  |  |  |  |  |

| DEC       | デコーダ                           | Y レジスタの内容を C 出力ポートの端子番号に変換して指定。<br>たとえば、 Y = 5 の場合、CO 5 の端子が指定。                                                                |  |  |  |  |  |  |

| PLA       | プログラマブル・ロジック<br>アレイ            | 論理素子がアレイ状に配列されている構造の積和論理回路で、プログラム可能。<br>4 ビットのデータと1つのフラグ (PS) 計5 ビットのデータを24 種の任意の8 ビットデータに変換。                                  |  |  |  |  |  |  |

| SP        | スタックポイント                       | スタックのアドレスを指定するレジスタ。                                                                                                            |  |  |  |  |  |  |

| MPX       | マルチプレクサ                        | 単一のデータ通路を、多数のデータ入出力が時分割の方法<br>で共有し、データ転送のオペレーションを行なう。                                                                          |  |  |  |  |  |  |

| SF        | センスフリップフロップ                    | CSLCTがL レベルのときカウンタの最上位桁が1から0になるとき(あふれたとき) セット。 CSLCT が H レベルのとき SNS 1 端子が H レベルになると SF がセット。 SF の状態 はブランチ命令 (BS 1 など)によって検出可能。 |  |  |  |  |  |  |

| E/D FF    | カウンタイネーブル/ディスエー<br>ブル・フリップフロップ | 命令 EC,DC によってセット,リセットされ外部信号を<br>カウントおよびストップの状態にする。                                                                             |  |  |  |  |  |  |

| S         | 同期化回路                          | カウンタとカウンタ信号入力の同期をとり SF にセット信号を送る。                                                                                              |  |  |  |  |  |  |

| G         | ダート                            | 複数個の入力端子と1個の出力端子を有し、ある入力条件<br>が満足された場合にだけ出力が出る回路。                                                                              |  |  |  |  |  |  |

| С         | コンペア                           | 2つのデータを比較判別する回路。<br>データの入っているメモリやレジスタの内容は変化しない。                                                                                |  |  |  |  |  |  |

| T/C       | ツルース/コンプリメント                   | 命令によって,データをそのまま転送したり,または各ビットの1と0を反転させ補数を求める回路。                                                                                 |  |  |  |  |  |  |

| CLOCK GEN | クロックゼネレータ                      | 動作に必要なクロック信号発生のための発振回路。<br>内部タイミング信号は、CP1、CP2、CP3の3相から構成。                                                                      |  |  |  |  |  |  |

| AI0~3     | A入力ポート                         | 4 ビット並列の入力ポート。                                                                                                                 |  |  |  |  |  |  |

| BI0~3     | B入力ポート                         | 4 ビット並列の入力ポート。                                                                                                                 |  |  |  |  |  |  |

| SNS0      | センス入力端子                        | 入力レベルによって条件ジャンプ(ブランチ)を実行。                                                                                                      |  |  |  |  |  |  |

| SNS1      | センス入力端子                        | CSLCT 端子との組合わせにより、SF への入力端子と、<br>内蔵カウンタへの入力端子の 2 通りの使い方が可能。                                                                    |  |  |  |  |  |  |

| CSLCT     | カウンタセレクト入力端子                   | SNS1端子の機能を切り換える端子。<br>L レベルのとき SNS1はカウンタ入力端子,H レベルの<br>とき SNS1はセンス入力端子。                                                        |  |  |  |  |  |  |

# 6932852 PANASONIC INDL. ELECTRONIC 72C 05686 D マイクロコンピュータ(4-Bit) 7-49-/9-04 MN1400 Family

| 記 号             | ブロック名     | 機能説明                                                                                                                    |

|-----------------|-----------|-------------------------------------------------------------------------------------------------------------------------|

| RST             | リセット入力端子  | L レベルのとき、プログラムカウンタ、すべての出力ラッチ、フラグ、センスフリップフロップ、カウンタイネーブルフリップフロップをクリアあるいはリセット。                                             |

| RST<br>(Pチャンネル) | リセット入力端子  | H レベルのとき、プログラムカウンタ、すべての出力ラッチ、フラグ、センスフリップフロップ、カウンタイネーブル・フリップフロップをクリアあるいはリセット。                                            |

| osc             | オシレータ入力端子 | クロック信号発生のための端子で、抵抗、コンデンサ各1個を接続すると、LSI内蔵の発振回路により必要なクロックが得られる。また、外部から約300kHz(200kHz: P-ch)の信号を入力すると、その信号に同期したクロック信号が得られる。 |

| TST<br>(TST)    | テスト入力端子   | LSIのテスト用端子。使用時は Vss に接続。                                                                                                |

| V <sub>DD</sub> | 電源入力端子    | V <sub>DD</sub> 電圧を印加 する。(標準+5V)                                                                                        |

| Vss             | 電源入力端子    | 接地する。(通常 0 V)                                                                                                           |

| CO0~11          | C出力ポート    | 12 本の個別出力 (ディスクリート出力)                                                                                                   |

| DO0~7           | D出力ポート    | プログラム可能な出力デコード回路 (PLA) で,5ビット<br>のデータを任意の8ビットのデータに変換し出力。<br>8ビット出力データの種類は最大24。                                          |

| EO0~3           | E出力ポート    | 4 ビット並列の出力ポート。                                                                                                          |

# 6932852 PANASONIC INDL, ELECTRONIC マイクロコンピュータ(4-Bit)

72C 05687 D MN1400 Family

■ MN1400ファミリ命令セット/MN1400 Family Instruction Set

T-49-19-04

|   | · · · · · · · · · · · · · · · · · · · |                             | 命令コード |        | 影響     |            |                                             |

|---|---------------------------------------|-----------------------------|-------|--------|--------|------------|---------------------------------------------|

|   |                                       | ニーモニック                      |       | 2 進コード |        | される<br>フラグ | 動作                                          |

|   | L                                     | load                        | 0000  | 1101   | 0D     | ZF         | A←M (X, Y)                                  |

|   | LD                                    | load direct                 | 0010  | 00 n   | 2n     | ZF         | A←M (0, n)                                  |

|   | LI                                    | load immediate              | 0101  | n      | 5n     | ZF         | A←n                                         |

|   | LIC                                   | *load increment Y           | 0000  | 1110   | 0E     | ZF         | $A \leftarrow M(X, Y), Y \leftarrow Y + 1$  |

|   | LDC                                   | *load decrement Y           | 0000  | 1111   | 0F     | ZF         | $A \leftarrow M(X, Y), Y \leftarrow Y - 1$  |

| テ | ST                                    | store                       | 0000  | 1010   | 0A     |            | M (X, Y)←A                                  |

| i | STD                                   | store direct                | 0010  | 01 n   | 2(4+n) |            | M (0, n)←A                                  |

| 9 | STIC                                  | *store increment Y          | 0000  | 1011   | 0B     | ZF         | $M(X, Y) \leftarrow A, Y \leftarrow Y + 1$  |

|   | STDC                                  | *store decrement Y          | 0000  | 1100   | 0C     | ZF         | $M(X, Y) \leftarrow A, Y \leftarrow Y - 1$  |

| 転 | LX                                    | load X                      | 0011  | 0 n    | 3n     |            | X←n                                         |

| 送 | LY                                    | load Y                      | 0110  | n      | 6n     |            | Y←n                                         |

| 命 | TAX                                   | transfar A to X             | 0000  | 0001   | 01     |            | X←A                                         |

| 令 | TAY                                   | transfer A to Y             | 0000  | 0011   | 03     |            | Y←A                                         |

| 1 | TYA                                   | transfer Y to A             | 0000  | 0010   | 02     | ZF         | A←Y                                         |

| l | TACU                                  | transfer A to counter upper | 0001  | 1001   | 19     |            | CU ←A                                       |

|   | TACL                                  | transfer A to counter lower | 0001  | 1000   | 18     |            | CL←A                                        |

|   | TCAU                                  | transfer counter upper to A | 0001  | 1011   | 1B     | ZF         | A←CU                                        |

|   | TCAL                                  | transfer counter lower to A | 0001  | 1010   | 1A     | ZF         | A←CL                                        |

|   | NOP                                   | no operation                | 0000  | 0000   | 00     |            |                                             |

|   | AND                                   | and                         | 0000  | 0100   | 04     | ZF         | $A \leftarrow A \wedge M(X, Y)$             |

|   | ANDI                                  | and immediate               | 0111  | n      | 7n     | ZF         | A←A∧n                                       |

| 1 | OR                                    | or .                        | 0000  | 0101   | 05     | ZF         | $A \leftarrow A \lor M(X, Y)$               |

| 1 | XOR                                   | exclusive or                | 0000  | 0110   | 06 .   | ZF         | $A \leftarrow A \forall M (X, Y)$           |

| 各 | A                                     | add                         | 0000  | 0111   | 07     | CF ZF      | $A \leftarrow A + M(X, Y) + CF$             |

| 種 | AI                                    | add immediate               | 1000  | n      | 8n     | CF ZF      | A←A+n                                       |

| 操 | CPL                                   | complement                  | 0000  | 1000   | 08     | ZF.        | A←Ā                                         |

| 作 | C                                     | compare                     | 0000  | 1001   | 09     | CF ZF      | $\overline{A}+M(X, Y)+1$                    |

|   | CI                                    | compare immediate           | 1001  | n      | 9n     | CF ZF      | A+n+1                                       |

| 命 | CY                                    | compare Y                   | 1010  | n      | An     | ZF         | Y∀n                                         |

| 令 | SL                                    | shift                       | 0001  | 1110   | 1E     | CF ZF      | A←A+A                                       |

|   | ICY                                   | increment Y                 | 0010  | 1100   | 2C     | ZF         | Y <b>←</b> Y+1                              |

|   | DCY                                   | decrement Y                 | 0010  | 1101   | 2D     | ZF         | Y <b>←</b> Y−1                              |

|   | ICM                                   | *increment memory           | 0010  | 1110   | 2E     | CF ZF      | $M(X, Y) \leftarrow M(X, Y) + 1$            |

|   | DCM                                   | *decrement memory           | 0010  | 1111   | 2F     | CF ZF      | M(X, Y)-M(X, Y)-1                           |

|   | SM                                    | *set memory bits            | 1011  | n      | Bn     |            | $M(X, Y) \leftarrow M(X, Y) \vee n$         |

| . | RM                                    | *reset memory bits .        | 1100  | n      | Cn     |            | $M(X, Y) \leftarrow M(X, Y) \wedge \bar{n}$ |

|   | TB                                    | test bits                   | 1101  | n      | Dn     | ZF         | A^n                                         |

<sup>\* 1</sup>バイト2サイクル命令 (ROM 1バイト使用 実行時間 20 μs(標準))

<sup>\*\*2</sup>パイト2サイクル命令 (ROM 2パイト使用 実行時間 20 μs (標準))

<sup>\*</sup>または\*\*を付さない命令は ROM 1パイト使用 実行時間 10 µs (標準)

6932852 PANASONIC INDL. ELECTRONIC マイクロコンピュータ(4-Bit)

T-49-19-04

MN1400 Family

∧ 論理積 (AND) ∨ 論理和 (OR) ∀ 排他的論理和 (XOR)

**72C** 05688

| -  |             |                                      | 論理和(OR) ♥ 辨他的論理和(XOR) |                   |                  |                   |                                                                                                                  |

|----|-------------|--------------------------------------|-----------------------|-------------------|------------------|-------------------|------------------------------------------------------------------------------------------------------------------|

|    |             | ニーモニック                               | 2 准コード 16             |                   | ド<br>16 進<br>コード | 影 響<br>される<br>フラグ | 動 作                                                                                                              |

|    | INA         | input via A-port                     | 0001                  | 0100              | 14               | ZF                | A←A-port                                                                                                         |

|    | INB         | input via B-port                     | 0001                  | 0101              | 15               | ZF                | A←B-port                                                                                                         |

| 入  | OTD         | output to D-port                     | 0001                  | 0010              | 12               |                   | D-port←A, PS                                                                                                     |

| 出  | ОТМО        | output memory to D-port              | 0001                  | 0001              | 11               |                   | D-port←M(X, Y), PS                                                                                               |

| カ  | OTE         | output to E-port                     | 0001                  | 0000              | 10               |                   | E-port←A                                                                                                         |

| 命  | OTIE        | output immediate to E-port           | 1111                  | n                 | Fn               |                   | E-port←n                                                                                                         |

| 令  | RCO         | reset C-port                         | 0001                  | 0110              | 16               |                   | C-port(Y)←0                                                                                                      |

| 1, | SC0         | set C-port                           | 0001                  | 0111              | 17               |                   | C-port(Y)←1                                                                                                      |

|    | CCO         | -                                    | 0001                  | 0011              | 13               |                   | C-port(11~0)←0                                                                                                   |

|    |             | clear C-port                         |                       |                   |                  |                   |                                                                                                                  |

|    | RC          | reset CF                             | 0010                  | 1000              | 28               | CF                | CF←0                                                                                                             |

|    | RP          | reset PS                             | 0010                  | 1001              | 29               | PS                | PS←0                                                                                                             |

|    | SC          | set CF                               | 0010                  | 1010              | 2A               | CF                | CF←1                                                                                                             |

|    | SP          | set PS                               | 0010<br>0011          | 1011<br>1011      | 2B<br>3B mm      | PS                | PS←1<br>  PC(7~0)←mm if SNS0=1                                                                                   |

|    | BS0         | **branch if SNS0=1  **branch if SF=1 | 0011<br>0011          | m                 | 3D mm            |                   | $PC(7\sim0)\leftarrow mm$ if $SF=1$                                                                              |

|    | BS1<br>BS01 | **branch if SNS0=1 or SF=1           | 0011                  | 1101<br>m<br>1111 | 3F mm            |                   | $PC(7\sim0)\leftarrow mm$ if $SNS0 \lor SF=1$                                                                    |

|    | BSN0        | **branch if SNS0=0                   | 0011<br>0011          | 1010              | 3A mm            |                   | $PC(7\sim0)\leftarrow mm \text{ if } SNS0=0$                                                                     |

|    | BSN1        | **branch if SF=0                     | 0011                  | 1100              | 3C mm            |                   | PC(7~0)←mm if SF=0                                                                                               |

|    | BSN01       | **branch if SNS0=0 and SF=0          | 0011                  | 1110              | 3E mm            |                   | $PC(7\sim0)\leftarrow mm$ if $SNS0 \lor SF=0$                                                                    |

| _  | BP          | **branch if PS=1                     | m                     | 1001              | E9 mm            |                   | PC(7~0)←mm if PS=1                                                                                               |

| _  | BC          | **branch if CF=1                     | 1110<br>1110          | 0101              | E5 mm            |                   | $PC(7\sim0)\leftarrow mm \text{ if } CF=1$                                                                       |

| ン  | BZ          | **branch if ZF=1                     | 1110                  | 0011              | E3 mm            |                   | PC(7~0)←mm if ZF=1                                                                                               |

| ŀ  | BPC         | **branch if PS=1 or CF=1             | m<br>1110             | m<br>1101         | EDmm             |                   | PC(7~0)←mm if PS∨CF=1                                                                                            |

|    | BPZ         | **branch if PS=1 or ZF=1             | 1110                  | 1011              | EB mm            |                   | PC(7~0)←mm if PS ∨ ZF=1                                                                                          |

| _  | BCZ         | **branch if CF=1 or ZF=1             | 1110                  | 0111              | E7 mm            |                   | PC(7~0)←mm if CF ∨ ZF=1                                                                                          |

| 1  | BPCZ        | **branch if PS=1 or<br>CF=1 or ZF=1  | 1110<br>m             | 1111<br>m         | EF mm            |                   | $PC(7\sim0)\leftarrow mm \text{ if } PS \lor CF \lor ZF=1$                                                       |

| ル  | BNP         | **branch if PS=0                     | 1110                  | 1000              | E8 mm            |                   | PC(7~0)←mm if PS=0                                                                                               |

| 命  | BNC         | **branch if CF=0                     | 1110                  | 0100              | E4 mm            | ļ                 | PC(7~0)←mm if CF=0                                                                                               |

| 令  | BNZ         | **branch if ZF=0                     | 1110                  | 0010              | E2 mm            |                   | $PC(7\sim0)\leftarrow_{mm} \text{ if } ZF=0$                                                                     |

|    | BNPC        | **branch if PS=0 and CF=0            | 1100<br>m             | 1100<br>m         | ECmm             |                   | $PC(7\sim0)\leftarrow mm \text{ if } PS \lor CF=0$                                                               |

|    | BNPZ        | **branch if PS=0 and ZF=0            | 1110                  | 1010              | EAmm             |                   | $PC(7\sim0)\leftarrow mm \text{ if } PS \lor ZF=0$                                                               |

|    | BNCZ        | **branch if CF=0 and ZF=0            | 1110                  | 0110<br>m         | E6 mm            |                   | $PC(7\sim0)\leftarrow mm \text{ if } CF\vee ZF=0$                                                                |

|    | BNPCZ       | **branch if PS=0, CF=0<br>and ZF=0   | 1110<br>m             | 1110<br>m         | EEmm             |                   | $ PC(7\sim0) \leftarrow mm \text{ if } PS \lor CF \lor ZF=0 $                                                    |

|    | JMP         | **jump                               | 0100<br>m             | On<br>m           | 4n mm            |                   | PC(10~8)←n, PC(7~0)←mm                                                                                           |

|    | CAL         | **call                               | 0100<br>m             | 1n<br>m           | 4(8+n)<br>mm     |                   | $\begin{array}{c} STACK \leftarrow PC + 2 \\ PC(10 \sim 8) \leftarrow n, PC(7 \sim 0) \leftarrow mm \end{array}$ |

|    | RET         | return                               | 0001                  | 1111              | 1F               |                   | PC(10~0)←STACK                                                                                                   |

|    | EC          | enable counter                       | 0001                  | 1101              | 1D               |                   |                                                                                                                  |

|    | DC          | disable counter                      | 0001                  | 1100              | 1C               |                   |                                                                                                                  |