# FastMATH™/FastMIPS™ Evaluation Kit

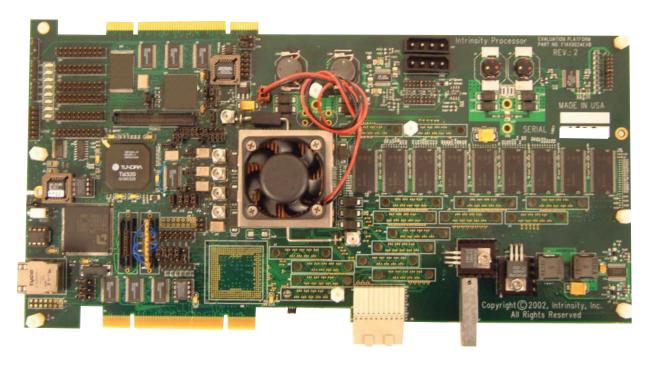

**Figure 1: Intrinsity Evaluation Board**

#### **CONTENTS**

| Overview                  | 1 |

|---------------------------|---|

| Modes of Operation        | 2 |

| Evaluation Board Features | 2 |

| Evaluation Kit Contents   | 2 |

| Board Form Factor         | 5 |

| External Interfaces       | 5 |

| Configuration Settings    | 6 |

| Test and Debug Interfaces | 6 |

| JTAG/EJTAG Scan Support   | 7 |

| Firmware                  | 7 |

| Acronyms & Abbreviations  | 7 |

| How to Reach Us           | 8 |

| Legal Notices             | 8 |

|                           |   |

## **Overview**

The Intrinsity™ FastMATH™/FastMIPS™ evaluation platform has been developed to facilitate rapid analysis of the Intrinsity FastMATH/FastMIPS processors. The platform may be used to perform a variety of functions including:

- Processor functionality assessment

- Performance analysis

- · Algorithm and software development

- Software and hardware tools evaluation

- Interfacing to PCI and RapidIO-based devices

Software tools provided include:

- C compiler

Version 1.1 Page 1 of 8

- Debugger

- Advanced matrix and vector math function libraries

- Power-on self-test diagnostics

- Evaluation software CD-ROMs from selected third-party vendors, including Green Hills Software

- Demo software

Extensive documentation is provided with the evaluation kit, including a user's guide and comprehensive processor documentation.

# **Modes of Operation**

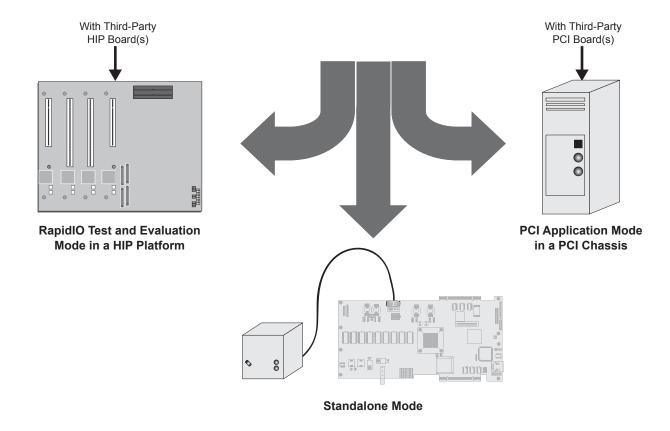

The evaluation platform supports three operational modes: standalone, RapidIO test and evaluation, and PCI application.

- Standalone mode

- Evaluation platform is placed on a bench and connected to the external power supply

- No connection is made to the external PCI interfaces

- RapidIO test and evaluation mode

- Evaluation platform is inserted into a RapidIO HIP baseboard

- PCI application mode

- Evaluation platform is inserted into a standard PCI slot and acts as a PCI target

**Note:** In each of the three operating modes, the board is powered by connecting it to a standard PC power supply using a hard drive power connector.

## **Evaluation Board Features**

The evaluation board includes the following features:

- FastMATH processor configurable for emulation of a FastMIPS processor

- Full-length PCI card form factor

- RapidIO<sup>™</sup> host interoperability platform (HIP) compatible

- Dual PCI connector support (top and bottom of printed circuit board)

- Approximately two inches taller than PCI standard

- 32-bit, 3.3-volt, 5-volt tolerant, PCI 2.2-compatible interface operates at up to 33 MHz

- AMD™ Am79c973 10/100 PCI ethernet controller PCI 2.2-compatible interface

- 128-Mbytes of DDR-333 synchronous dynamic random-access memory (SDRAM) standard

- General purpose I/O (GPIO) subsystem

- Field programmable gate array (FPGA) for miscellaneous system functions, including test registers, I<sup>2</sup>C® interface, and universal asynchronous receiver/transmitter (UART)

- 8-Mbytes of flash memory

- PromICE® interface

- 8 status light-emitting diodes (LEDs)

- MIPS® Extended Joint Test Action Group (EJTAG) revision 2.60-compliant debug interface connection

- Logic analyzer visibility and connection mechanism provided for all interfaces

# **Evaluation Kit Contents**

The Intrinsity evaluation kit contains the following items:

Page 2 of 8 Version 1.1

- Intrinsity Evaluation Kit Getting Started Guide

- Intrinsity Evaluation Board User's Guide

- Evaluation board with processor and memory

- Intrinsity software and documentation CD-ROM

- Third-party evaluation software CD-ROM or CD-ROMs

- Extra jumpers

- Serial port dongle

- Gender changer

- DB-9-to-DB-9 serial cable

- Power supply

## **Additional Hardware and Software Requirements**

To use the Intrinsity evaluation board, you will need to provide the following:

- Serial terminal emulation software or ethernet network with a host running telnet

- EJTAG debug probe (optional)

Figure 2: Evaluation platform modes of operation

Version 1.1 Page 3 of 8

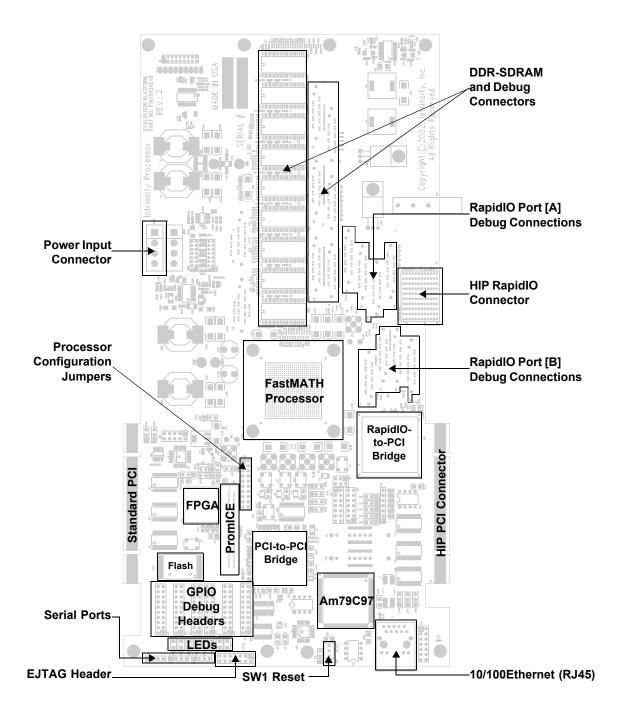

Figure 3: The FastMATH/FastMIPS evaluation platform

Page 4 of 8 Version 1.1

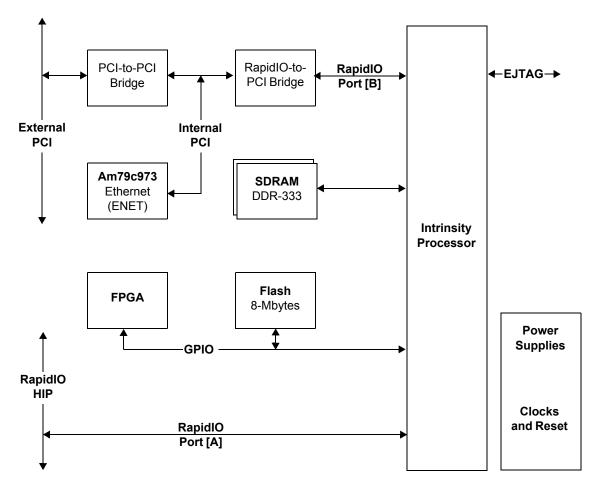

Figure 4: Evaluation platform block diagram

## **Board Form Factor**

The format factor of the design is a dual-edged, long PCI card that includes the RapidIO HIP connectors along one side. The card is approximately 2-inches taller than a standard PCI card. Figure 3 on page 4 shows the physical outline of the board.

Including the HIP PCI connector, the evaluation board is 12.3-inches long by 6.4-inches wide.

## **External Interfaces**

The evaluation platform includes five types of external interfaces: PCI, RapidIO HIP, serial ports, 10/100Base-T Ethernet, and flash ROM emulation.

PCI interface

There are two PCI interfaces in the evaluation platform to allow insertion in a standard PCI slot or RapidIO HIP platform slot. The PCI interfaces are 32 bits wide, operating at 33-MHz. The PCI interfaces are 5-volt tolerant and can plug into 5-volt or 3-volt PCI slots. When the standard PCI edge connector is used, most components are on the opposite side of the board from what the PCI specification recommends; thus, the board consumes more than one PCI slot.

RapidIO HIP interface

One of the processor's RapidIO ports is connected directly to a high-speed differential connector, located on the bottom of the evaluation board for use in a RapidIO hardware interoperability platform.

Version 1.1 Page 5 of 8

The design of the evaluation board and the HIP platform allow operation of both the RapidIO and one of the PCI interfaces when the evaluation board is plugged into the HIP baseboard.

Serial ports

The board includes a standard serial port interface. No hardware flow or modem control signals are provided. The signals are connected to standard Berg 4-pin headers. The evaluation kit includes a DB-9 serial port dongle that plugs into this header.

10/100Base-T ethernet interface

A standard 10/100Base-T UTP Ethernet interface is provided on an RJ45 connector. The interface is wired as a transceiver port so that a direct connect Category 5 cable can be used to connect to a hub or to a switch port on a LAN. If the evaluation platform is to be connected directly to a computer, then a Category 5 crossover cable is required.

Flash ROM emulation interface

Flash emulation is accomplished using a 60-pin header that can be connected to a ROM emulator. Use of the ROM emulator is enabled via a jumper setting. The pinout conforms to the PromICE™ pin outs defined by Grammar Engine, Inc. (http://www.gei.com/).

# **Configuration Settings**

There are options for setting the operational mode of the board, as well as processor-specific configuration. Most configuration is done with jumpers.

Operational mode

Standalone mode is jumper selectable. PCI or HIP modes are detected when the board is plugged in to a system. If the board is plugged into a HIP system that does not provide PCI slots, the user should enable standalone mode.

Processor configuration

The processor configuration is jumper selectable and includes the following modes of operation:

- Force FastMIPS emulation mode

- Big or little endian mode

SDRAM clock frequency is a derivative of the core processor frequency and is jumper selectable.

# **Test and Debug Interfaces**

The board provides pre-defined connections to test equipment for debug and test.

Processor interface

All processor interface signals are visible to the user via logic analyzer connections provided on the evaluation platform. Many of these are accomplished by special land patterns designed specifically for the *Tektronix TLA7xx series* equipment.

RapidIO interface

There are two RapidIO interfaces. Land patterns for the *Tektronix P6880 high-density differential probes* have been provided for each port. Each port consumes a single 136-channel module and requires probes. These connections are intended for use with the *Tektronix RapidIO Support Package*.

DDR-SDRAM

The DDR-SDRAM interface can be instrumented by using *Tektronix P6860* probes. There are a total of 112 signal pins visible on this interface.

General Purpose I/O (GPIO)

The GPIO chip-select interface and FPGA signals have been brought out to several Berg style 0.1-inch headers. This allows the user maximum flexibility when assigning channels to the logic analyzer.

Page 6 of 8 Version 1.1

Internal PCI

The internal PCI bus may be monitored using a standard Mictor connector pin out as specified by Tektronix and New Wave (http://www.busboards.com/). The IDSEL field may be configured to point to the on-board Ethernet MAC, RapidIO-PCI Bridge, or PCI-PCI Bridge.

Temperature Sensor

A temperature sensor is connected to the FastMATH processor. This device, National LM86, has a two wire serial interface that may be accessed through one of two I<sup>2</sup>C master interfaces: one in the RapidIO-to-PCI bridge chip and one in the FPGA.

# **JTAG/EJTAG Scan Support**

JTAG headers are provided for direct access to the major scanable devices in the evaluation board.

### **Firmware**

Included with the evaluation platform is a resident firmware package based on RedBoot firmware. It provides a complete bootstrap environment and includes facilities such as network downloading and debugging. RedBoot firmware provides a wide set of tools for downloading and executing programs on evaluation platform, as well as tools for manipulating the target system's environment. It can be used for both product development (debug support) and for end product deployment (flash and network booting).

Some highlights of the capabilities include:

- Simple command line interface accessible via serial port (terminal) or Ethernet (telnet)

- Integrated gdb stubs for connection to a host-based debugger via serial or Ethernet

- Power-on self-test

- Initialization of primary FastMATH/FastMIPS subsystems such as RapidIO, SDRAM, etc.

- Boot scripting support

- Configuration management of user control of aspects such as default flash image to boot from, default fail-safe image, static IP address, etc.

- Network bootstrap support including setup and download via BOOTP and TFTP

- X/YModem support for image download via serial port

The evaluation platform firmware is supplied in object form in the on-board flash memory. Source is available on request.

# **Acronyms & Abbreviations**

DDR double data-rate

FPGA field-programmable gate array

GPIO general purpose input/output

HIP hardware interoperability platform

PCI peripheral component interconnect

PLL phase lock loop

SDRAM synchronous dynamic random access memory

SMA surface mount attach

UART universal asynchronous receiver-transmitter

UTP unshielded twisted pair

Version 1.1 Page 7 of 8

## **How to Reach Us**

#### **WEB SITE:**

www.intrinsity.com

#### **TECHNICAL SUPPORT EMAIL:**

techsupport@intrinsity.com

#### **USA & LOCATIONS NOT LISTED:**

Intrinsity, Inc.

11612 Bee Caves Road

Building II, Suite 200

Austin, TX 78738

512 421 2100 voice

512 263 0795 fax

sales-us@intrinsity.com

sales-asia@intrinsity.com

#### **EUROPE**:

Intrinsity International, Inc. P. O. Box 157

Banbury

OX17 2ZJ

England

+44 0 1295 712164 voice

+44 0 1295 712913 fax

sales-europe@intrinsity.com

#### JAPAN:

Intrinsity International, Inc. 1-5-6 Kanda-Surugadai Kotoh Surugadai #213 Chiyoda-ku, Tokyo 101-0062, Japan +81 3 5282 5411 voice +81 3 5282 5412 fax sales-japan@intrinsity.com

#### **Revision History**

Version 0.9.3

.20 December 2002

Version 1.0

.27 January 2003

Version 1.1

.24 March 2003

Copyright © 2002-2003 Intrinsity, Inc. All rights reserved.

Information in this document is provided solely to enable system and software implementers to use Intrinsity products. Intrinsity reserves the right to make changes without further notice to any products mentioned herein.

INTRINSITY MAKES NO WARRANTY, REPRESENTATION, OR GUARANTEE REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR DOES INTRINSITY ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT, AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY, INCLUDING WITHOUT LIMITATION CONSEQUENTIAL OR INCIDENTAL DAMAGES. Parameters that may be provided in Intrinsity data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters must be validated for each customer application by customer's technical experts. Intrinsity does not convey any license under its patent rights nor the rights of others. Intrinsity assumes no liability or obligation for damages of any kind arising our of the application of use of these materials. Any warranty or other obligations as to the products described herein shall be undertaken solely by the marketing party to the customer, under a separate sale agreement between the marketing party and the customer, in the absence of such an agreement, no liability is assumed by Intrinsity or the marketing party for any damages, actual or otherwise.

Intrinsity makes no claim, warranty, or representation, express or implied that the products described in this document are designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the product could create a situation where personal injury or death may occur. Should customer purchase or use the products for any such unintended of unauthorized application, customer shall indemnify and hold Intrinsity and their respective officers, employees, subsidiaries, affiliates, and distributes harmless against all claims, costs, damages, and expenses, and reasonable attorney's fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Intrinsity was negligent regarding the design or manufacture of the part.

Any and all information, including technical data, computer software, documentation or other commercial material contained in or delivered in conjunction with this document (collectively, "Technical Data") were developed exclusively at private expense, and such Technical Data is made up entirely of commercial items and/or commercial computer software. Any and all Technical Data that may be delivered to the United States Government or any governmental agency or political subdivision of the United States Government (the "Government") are delivered with restricted rights in accordance with Subpart 12.2 of the Federal Acquisition Regulation and Parts 227 and 252 of the Defense Federal Acquisition Regulation Supplement. The use of Technical Data is restricted in accordance with the terms set forth herein and the terms of any license agreement(s) and/or contract terms and conditions covering information containing Technical Data received between Intrinsity or any third party and the Government, and the Government is granted no rights in the Technical Data except as may be provided expressly in such documents.

Intrinsity, the Intrinsity logo, the Intrinsity dot logo, and FastMATH are trademarks and/or registered trademarks of Intrinsity, Inc. in the United States and/or other countries. MIPS, MIPS32, MIPS-based, and FastMIPS are trademarks and/or registered trademarks of MIPS Technologies, Inc. RapidIO is a trademark of the RapidIO Trade Association. RedBoot is a trademark of RedHat, Inc. PromICE is a trademark of Grammar Engine, Inc. All other trademarks/registered trademarks are the property of their respective owners.

Page 8 of 8 Version 1.1