### $\mu$ COM-42 4-BIT SINGLE CHIP MICROCOMPUTER

#### **DESCRIPTION**

The  $\mu$ COM-42 (Part No.  $\mu$ PD548) is a single chip microcomputer that is ideally suited for Electronic Cash Register (ECR), Point of Sale (POS) and Electronic Scale applications.

Containing a 4-bit Parallel ALU, ROM for program storage and RAM for data storage, the  $\mu$ COM-42 provides an economical and simple solution to many Vending/Calculating requirements.

Because of its extensive instruction set and five input/output ports, the  $\mu$ COM-42 is capable of controlling an  $8\times4$  keyboard, an 8 digit display and low cost ECR-type printers.

Finally, the on-chip RAM space can be augmented by an external CMOS RAM for applications requiring low power data retention.

#### **FEATURES**

- Stand Alone 4-bit Microcomputer

- All 72 Instructions are Single Byte

- 10 µsec Instruction Cycle

- 1920 x 10-Bit Program Memory (ROM)

- 96 x 4-Bit Data Memory (RAM)

- 4-Level Stack

- 2 Interrupt Request Lines

- I/O Compatible with TTL

- 10 Discrete Output Ports (F<sub>0</sub>-F<sub>9</sub>)

- Two 8-Bit Output Ports (U<sub>0</sub>-U<sub>7</sub>, R<sub>0</sub>-R<sub>7</sub>)

- One 4-Bit Input Port (K<sub>0</sub>-K<sub>3</sub>)

- One 4-Bit Input/Output Port (S<sub>0</sub>-S<sub>3</sub>)

- One Single Bit Testable Input Port (K<sub>4</sub>)

- Single Phase TTL Level Clock (200 KHz Max.)

- Single Supply, -10V PMOS Technology

- 42 Pin Plastic Dual-in-Line Package

#### PIN CONFIGURATION

| RES 🗖 1                     | <b>–</b> | 42 <b>□</b> φ              |

|-----------------------------|----------|----------------------------|

| K <sub>0</sub> ☐ 2          |          | 41 VGG(-1                  |

| к₁ 🗖 з                      |          | 40 <b>6</b> K4             |

| K2 ☐ 4                      |          | 39 <b>5</b> R 7            |

| K <sub>3</sub> 🗍 5          |          | 38 <b>G</b> R <sub>6</sub> |

| TEST 6                      |          | 37 B R5                    |

|                             |          |                            |

| - 0                         |          | 36 R4                      |

| S1 ☐ 8                      |          | 35 R3                      |

| S <sub>2</sub> 📙 9          |          | 34 <b>2</b> R2             |

| S3 🗖 10                     | $\mu$ PD | 33 🏳 R 1                   |

| IA 🔲 11                     | 548      | 32 🗖 R <sub>0</sub>        |

| IB 🗖 12                     | 540      | 31 🗖 U7                    |

| F <sub>0</sub> □ 13         |          | 30 ⊅ U <sub>6</sub>        |

| F1 🗖 14                     |          | 29 🗖 U5                    |

| F <sub>2</sub> 15           |          | 28 D U4                    |

| F <sub>3</sub> 16           |          | 27 5 03                    |

| F <sub>4</sub> 17           |          |                            |

|                             |          |                            |

| F5 18                       |          | 25 U1                      |

| F6 ☐ 19                     |          | 24 D U0                    |

| F <sub>7</sub> $\square$ 20 |          | 23 <b>F</b> 9              |

| GND 21                      |          | 22 T F8                    |

|                             |          |                            |

| PIN NAMES                        |                                                  |  |  |  |

|----------------------------------|--------------------------------------------------|--|--|--|

| RES                              | Reset                                            |  |  |  |

| K <sub>0</sub> -K <sub>3</sub>   | Input Port K                                     |  |  |  |

| TEST                             | Input for Testing<br>(Normally V <sub>GG</sub> ) |  |  |  |

| \$ <sub>0</sub> –\$ <sub>3</sub> | Input/Output Port S                              |  |  |  |

| IA, IB                           | Interrupt Input Ports                            |  |  |  |

| F <sub>0</sub> -F <sub>9</sub>   | Output Port F                                    |  |  |  |

| U <sub>0</sub> -U <sub>7</sub>   | Output Port U                                    |  |  |  |

| R <sub>0</sub> -R <sub>7</sub>   | Output Port R                                    |  |  |  |

| K4                               | Input Port for<br>Condition Test                 |  |  |  |

| ø                                | Clock Input                                      |  |  |  |

6

### μCOM-42

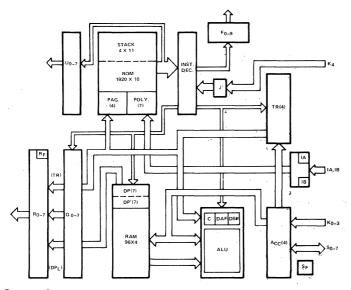

**BLOCK DIAGRAM**

**FUNCTIONAL DESCRIPTION**

#### **Program Counter**

The 11-bit program counter is composed of two sections, a 4-bit page register and a 7-bit polynomial counter. The page register selects one page out of 15, each consisting of 128 words addressed by the 7-bit polynomial counter. The contents of the page register are independent of the operation of the polynomial counter, so that it is not affected by polynomial counter overflow.

#### Stack Register

In order to store the program counter contents upon an interrupt or subroutine call, four 11-bit stack registers are provided to enable a combination of subroutine calls and interrupt nesting to four levels. The stack register is a LIFO (Last in, First-Out) type.

#### ROM (Read Only Memory)

The on-chip ROM consists of 1,920 words of ten bits each and is divided into 15 pages. A page is selected by the page register, the upper four bits of the program counter. Each page consists of 128 words addressed by the polynomial counter, the lower seven bits of the program counter.

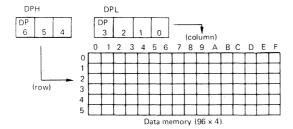

### RAM (Data Memory)

The data memory is a  $96 \times 4$ -bit RAM addressed by a 7-bit data pointer (DP). The RAM is divided into six rows of 16 4-bit columns each. The 7-bit data pointer consists of an upper 3-bit register (DPH) which selects the row address and a lower 4-bit register (DPL) which selects the column address.

# FUNCTIONAL DESCRIPTION (CONT.)

#### Internal Registers

The Accumulator (ACC) is connected with the ALU and the carry flip-flop (C) and is able to perform either binary or decimal arithmetic by testing the decimal addition flip-flop (DAF) and the decimal subtraction flip-flop (DSF). Constants are loaded into the ACC as immediate data from ROM and variable data are loaded from or exchanged with RAM. The ACC is also connected with the temporary register (TR), the parallel I/O port S and the parallel input port K. The TR is an auxiliary register used for temporary storage of 4-bit data. The Q register is an 8-bit serial-in/parallel-out shift register designed for display digit strobing and generation of printer hammer triggers.

#### I/O Ports

The R port is an 8-bit parallel port that may be loaded from the Q register for digit strobing or loaded with the 4-bit TR and the 4-bit DPL for external RAM addressing. The U port is an 8-bit parallel port that is loaded with immediate data. It is usually used for outputting segment information for display and digit information for key scanning. The K port is a 4-bit input port that is usually used for key scan input. The K4 port is a single bit port that is testable by software. The S port is a 4-bit parallel I/O port that is typically used as the data bus to external RAM. The F port consists of ten discrete output lines that can be individually set or reset under program control.

#### Interrupt Ports

Two interrupt input lines, IA and IB, are available to accept an interrupt request when interrupts are enabled. IA has a higher priority level than IB. Thus when concurrent interrupts occur on both IA and IB only the IA interrupt is accepted and both are disabled. But a single IB interrupt disables only the IB interrupt and leaves IA enabled.

#### **INSTRUCTION SET**

The  $\mu$ COM-42 has a powerful 72, 10-bit word, instruction set. All instructions are single words. There are a number of multi-function instructions which reduce the number of program steps. In addition, automatic data pointer modification, single word subroutine calls and N-way branch capability all help improve operation speed and reduce ROM requirements. The  $\mu$ COM-42 instruction set is summarized below.

| MNEMONIC CYCLES |     | DESCRIPTION                                                                                                                                                   | CONDITIONS<br>FOR SKIP                           |  |

|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|

| CMA             | 1   | A <sub>CC</sub> · (A <sub>CC</sub> )                                                                                                                          |                                                  |  |

| CIA             | 1   | A <sub>CC</sub> · (A <sub>CC</sub> ) + 1                                                                                                                      |                                                  |  |

| INA             | 1/2 | Acc · (Acc) + 1                                                                                                                                               | . Carry : 1                                      |  |

| DEA             | 1/2 | ACC · (ACC) - 1                                                                                                                                               | Borrow / 1                                       |  |

| RFC .           | 1   | . C · 0                                                                                                                                                       |                                                  |  |

| SFC             | 1   | C · 1                                                                                                                                                         |                                                  |  |

| DSM             | 1   | Decimal Subtract Mode .                                                                                                                                       |                                                  |  |

| DAM             | 1   | Decimal Add Mode                                                                                                                                              |                                                  |  |

| AD              | 1/2 | ACC · (ACC) + [DP]                                                                                                                                            | Carry - 1                                        |  |

| ADC             | 1   | . Acc. C - (Acc) + [DP] + (C)                                                                                                                                 |                                                  |  |

| ADI             | 1/2 | . ACC - (ACC) + I3 I2 I1 I0                                                                                                                                   | Carry ÷ 1                                        |  |

| LM              | 1   | A <sub>CC</sub> · [DP]<br>DP <sub>H</sub> · (DP <sub>H</sub> ) ∀ M <sub>2</sub> M <sub>1</sub> M <sub>0</sub>                                                 |                                                  |  |

| XM              | 1   | (A <sub>CC</sub> ) ·· [DP]<br>DP <sub>H</sub> · (DP <sub>H</sub> ) ∀ M <sub>2</sub> M <sub>1</sub> M <sub>0</sub>                                             |                                                  |  |

| XMI             | 1/2 | (A <sub>CC</sub> ) ·· [DP}<br>DP <sub>H</sub> · (DP <sub>H</sub> ) ∀ M <sub>2</sub> M <sub>1</sub> M <sub>0</sub><br>DP <sub>L</sub> · (DP <sub>L</sub> ) + 1 | (DP <sub>L</sub> ) = 8 or (DP <sub>L</sub> ) = 0 |  |

| XMD             | 1/2 | (A <sub>CC</sub> ) [DP], DP <sub>H</sub> · (DP <sub>H</sub> )<br>M <sub>2</sub> M <sub>1</sub> M <sub>0</sub> , DP <sub>L</sub> · (DP <sub>L</sub> ) - 1      | (DP <sub>L</sub> ) = F or (DP <sub>L</sub> ) - 7 |  |

| LI              | 1   | Acc · 13 12 11 10                                                                                                                                             |                                                  |  |

| LDI             | 1   | DP - 16-10                                                                                                                                                    |                                                  |  |

| IND             | 1/2 | DPL (DPL) + 1                                                                                                                                                 | (DP <sub>L</sub> ) = 8 or (DP <sub>L</sub> ) = 0 |  |

| DED             | 1/2 | DPL (DPL) 1                                                                                                                                                   | (DP <sub>L</sub> ) = F or (DP <sub>L</sub> ) - 7 |  |

| X DP            | 1   | (DP) · · (DP')                                                                                                                                                |                                                  |  |

| ZAG             | 1   | 000DP <sub>1</sub> ·· (DP)                                                                                                                                    |                                                  |  |

# μCOM-42

**INSTRUCTION SET**

| MNEMONIC | CYCLES                                           | CYCLES DESCRIPTION                                                                                                                   |                                        |

|----------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| XTA ,    | 1                                                | (A <sub>CC</sub> ) ↔ (TR)                                                                                                            |                                        |

| LTI      | 1                                                | TR ← I <sub>3</sub> I <sub>2</sub> I <sub>1</sub> I <sub>0</sub>                                                                     |                                        |

| Q\$1     | -1                                               | $Q_{n+1} \leftarrow Q_{n}, Q_0 \leftarrow 1$                                                                                         |                                        |

| QS0      | 1                                                | $Q_{n+1} \leftarrow Q_n, Q_0 \leftarrow 0$                                                                                           |                                        |

| SB .     | 1                                                | [DP, B <sub>1</sub> , B <sub>0</sub> ] ← 1                                                                                           |                                        |

| RB       | 1                                                | [DP, B <sub>1</sub> , B <sub>0</sub> ] ← 0                                                                                           |                                        |

| SBT      | 1/2                                              | Skip if [DP, B <sub>1</sub> , B <sub>0</sub> ] = 1                                                                                   | B <sub>1</sub> B <sub>0</sub> = 1      |

| SC       | 1/2                                              | Skip if (C) = 1                                                                                                                      | (C) = 1                                |

| SEM      | 1/2                                              | Skip if (A <sub>CC</sub> ) = [DP]                                                                                                    | (ACC) = [DP]                           |

| SEI      | 1/2                                              | Skip if (ACC) = 13 12 11 10                                                                                                          | (Acc) = 13 12 11 10                    |

| SK4      | 1/2                                              | Skip if K <sub>4</sub> = 1                                                                                                           | K <sub>4</sub> = 1                     |

| JPT      | 1                                                | PC ← (TR), P <sub>6</sub> -0                                                                                                         |                                        |

| JPA      | 1                                                | PC <sub>6-4</sub> ← P <sub>6-4</sub>                                                                                                 |                                        |

| JCP      | <del>                                     </del> | PC <sub>3-0</sub> ← P <sub>3-0</sub> V (A <sub>CC</sub> )                                                                            |                                        |

|          |                                                  | PC <sub>6-0</sub> ← P <sub>6-0</sub>                                                                                                 |                                        |

| CAL      | 1                                                | [STACK] ← (PC)<br>PC ← 1000 P <sub>6</sub> P <sub>5</sub> P <sub>4</sub> P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> |                                        |

| RT       | 1                                                | PC ← [STACK]                                                                                                                         |                                        |

| RTS      | 2                                                | PC ← [STACK]<br>PC ← (PC) + 1                                                                                                        |                                        |

| EIA .    | 1                                                | Enable IA port                                                                                                                       |                                        |

| DIA      | 1                                                | Disable IA port                                                                                                                      |                                        |

| EIB      | 1                                                | Enable IB port                                                                                                                       |                                        |

| DIB      | 1                                                | Disable IB port                                                                                                                      |                                        |

| OIU      | 1                                                | U <sub>7-0</sub> ← I <sub>7-0</sub>                                                                                                  |                                        |

| ERO      | <del>                                     </del> | R <sub>7-0</sub> ← (Q <sub>7-0</sub> )  Enable R port                                                                                |                                        |

| DRO      | <del>                                     </del> | Disable R port                                                                                                                       |                                        |

| OQR      | <del>                                     </del> | B ← (Q)                                                                                                                              | ······································ |

| OTR      | <del>                                     </del> |                                                                                                                                      |                                        |

| SFS      |                                                  | R <sub>7-4</sub> ← (TR), R <sub>3-0</sub> ← (DP <sub>L</sub> )                                                                       |                                        |

|          | 1 1                                              | S ← (ACC)                                                                                                                            |                                        |

| RFS      | 1 1                                              | S port Input Mode                                                                                                                    |                                        |

| IS       | 1                                                | Acc ← S                                                                                                                              |                                        |

| IK .     | 1                                                | Acc K                                                                                                                                |                                        |

| RF1      | 1                                                | F <sub>1</sub> ← 0                                                                                                                   |                                        |

| SF 1     | 1 1                                              | F <sub>1</sub> ← 1                                                                                                                   |                                        |

| RF2      | 1                                                | F <sub>2</sub> ← 0                                                                                                                   |                                        |

| SF2      | 1.                                               | F <sub>2</sub> -1                                                                                                                    |                                        |

| RF3      | 1 1                                              | F3 ← 0                                                                                                                               |                                        |

| SF3      | 1                                                | F <sub>3</sub> ← 1                                                                                                                   |                                        |

| RF4      | 1                                                | F4 ← 0                                                                                                                               |                                        |

| SF4      | 1                                                | F4 ← 1                                                                                                                               |                                        |

| RF5      | 1                                                | F5 ← 0                                                                                                                               |                                        |

| SF5      | 1                                                | F <sub>5</sub> ← 1                                                                                                                   |                                        |

| RF6      | 1                                                | F <sub>6</sub> + 0                                                                                                                   |                                        |

| SF6      | 1                                                | F <sub>6</sub> ← 1                                                                                                                   |                                        |

| RF7      | 1                                                | F <sub>7</sub> ← 0                                                                                                                   |                                        |

| SF7      | 1                                                | F <sub>7</sub> ← 1                                                                                                                   |                                        |

| RF8      | 1                                                | F <sub>8</sub> ←0                                                                                                                    |                                        |

| SF8      | . 1                                              | F <sub>8</sub> ← 1                                                                                                                   |                                        |

| RF9      | 1                                                | F <sub>9</sub> ← 0                                                                                                                   |                                        |

| SF9      | 1                                                | Fg ← 1                                                                                                                               |                                        |

| RF0      | 1                                                | F <sub>0</sub> ← 0                                                                                                                   |                                        |

| SF0      | 1                                                | F <sub>0</sub> ←1                                                                                                                    |                                        |

| NOP      | 1                                                | No Operation                                                                                                                         |                                        |

## $\mu$ COM-42 SINGLE CHIP MICROCOMPUTER

DESCRIPTION The  $\mu$ PD548 is the only version of the  $\mu$ COM-42. This PMOS, –10 volt part is designed to have TTL-level compatible inputs and was specifically designed for external RAM expansion. As a  $\mu\text{COM-42},$  it includes 1920 x 10 ROM, 96 x 4 RAM and 35 I/O lines in a 42 pin plastic dual-in-line package.

#### ABSOLUTE MAXIMUM **RATINGS\***

| Operating Temperature          | $-10^{\circ}$ C to $+70^{\circ}$ C |

|--------------------------------|------------------------------------|

| Storage Temperature            | -40°C to +125°C                    |

| Supply Voltage V <sub>GG</sub> | -15 to +0.3 Volts                  |

| Input Voltages                 | -40 to +0.3 Volts                  |

| Output Voltages                |                                    |

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device

${}^{*}T_{a} = 25^{\circ}C$

DC CHARACTERISTICS  $T_a = -10^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$ ;  $V_{GG} = -10\text{V} \pm 10\%$

|                               |                   | LIMITS |     |       |      | TEST                                |

|-------------------------------|-------------------|--------|-----|-------|------|-------------------------------------|

| PARAMETER                     | SYMBOL            | MIN    | TYP | MAX   | UNIT | CONDITIONS                          |

| Input High Voltage            | V <sub>IH</sub>   | 0      |     | - 2.0 | V    |                                     |

| Input Low Voltage             | VIL               | -4.3   |     | Vgg   | V    | •                                   |

| Output High Voltage           | V <sub>OH1</sub>  |        |     | - 3.0 | V    | IOH = -4 mA ①                       |

| Output High Voltage           | V <sub>OH2</sub>  | ,      | ,   | - 1.0 | V    | IOH = -1 mA<br>(for S port outputs) |

| Input Leakage<br>Current High | <sup>1</sup> LIH  |        |     | +10   | μΑ   | V <sub>I</sub> = -1V                |

| Input Leakage<br>Current Low  | ILIL              |        |     | -30   | μΑ   | V <sub>I</sub> = -36V               |

| Output Current High           | Іон               | -1.0   |     |       | mA   | V <sub>OH</sub> = -1V               |

| Output Leakage<br>Current Low | <sup>1</sup> LOL1 |        |     | -30   | μΑ   | V <sub>O</sub> = -36V               |

| Output Leakage<br>Current Low | LOL2              |        |     | -10   | μΑ   | $V_0 = -5V$<br>(for S port outputs) |

| Supply Current                | IGG               |        | -30 | -60   | mA   |                                     |

Note: 1 For Report, and when only 1 bit is ON (high level)

AC CHARACTERISTICS  $T_a = -10^{\circ} \text{C to } +70^{\circ} \text{C}$ ;  $V_{GG} = -10 \text{V} \pm 10\%$ , unless otherwise noted

|                      |        | LIMITS |     |     |      | TEST       |

|----------------------|--------|--------|-----|-----|------|------------|

| PARAMETER            | SYMBOL | MIN    | TYP | MAX | UNIT | CONDITIONS |

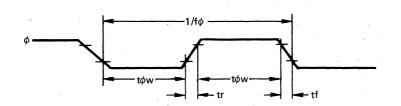

| Clock Frequency      | fφ     | 100    |     | 200 | KHz  |            |

| Clock Pulse Width    | tφw    | 2.25   |     |     | μs   |            |

| Clock Rise-Fall Time | tr, tf |        |     | 0.5 | μs   |            |

# **μ**PD548

$T_a = 25^{\circ}$ C;  $V_{GG} = -10V \pm 10\%$ , unless otherwise noted.

|                                     |                  | LIMITS |     |      |      | TEST                                      |

|-------------------------------------|------------------|--------|-----|------|------|-------------------------------------------|

| PARAMETER                           | SYMBOL           | MIN    | TYP | MAX  | UNIT | CONDITIONS                                |

| Capacitance, Any<br>Input Except S  | Cl               |        | 1.  | 15 🐇 | рБ⊘  |                                           |

| Capacitance, Any<br>Output Except S | C <sub>O</sub> , |        |     | 15   | pF   | f = 1 MHz                                 |

| S Port<br>Capacitance               | CIO              |        |     | 15   | pF   | er en |

### CAPACITANCE

**CLOCK WAVEFORM**

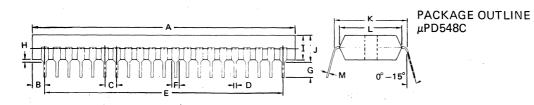

| ITEM | MILLIMETERS | INCHES       |  |

|------|-------------|--------------|--|

| Α    | 56.0 MAX    | 2.2 MAX      |  |

| В    | 2.6 MAX     | 0.1 MAX      |  |

| С    | 2.54        | 0.1          |  |

| D    | 0.5 ± 0.1   | 0.02 ± 0.004 |  |

| E    | 50.8        | 2.0          |  |

| F    | 1.5         | 0.059        |  |

| G    | 3.2 MIN     | 0.126 MIN    |  |

| н    | 0.5 MIN     | 0.02 MIN     |  |

| Ī    | 5.22 MAX    | 0.20 MAX     |  |

| J    | 5.72 MAX    | 0.22 MAX     |  |

| K    | 15.24       | 0.6          |  |

| L    | 13.2        | 0.52         |  |

| М    | 0.3 ± 0.1   | 0.01 ± 0.004 |  |