# 2 GHz FastMATH<sup>™</sup> and 1 GHz FastMATH-LP<sup>™</sup> Adaptive Signal Processor<sup>™</sup> Products

# **KEY BENEFITS**

- Unprecedented matrix and vector math performance enables implementation of time-critical signal processing algorithms in software

- Time-to-market improved since the complex and time-consuming task of designing and debugging custom hardware-based algorithm solutions is eliminated

- Programmable system architecture enables easy upgrades to comply with emerging standards

- Software-based system solutions give OEMs the opportunity to provide differentiating features

- MIPS® instruction set with broad tools and system software support

# Matrix MIPS32™ CPU 1MB Level 2 Cache SDRAM Control ION Ring™ Interconnect RapidIO™ DMA EJTAG GPIO RapidIO™ Port

# **FEATURES**

The first Adaptive Signal Processor™ products, integrating a native matrix/vector math unit, a high-performance RISC CPU, and high-bandwidth I/O architected to solve today's real-time, math-intensive, and adaptive signal processing problems.

2 GHz FastMATH processor (13.5W typ) for maximum

. 1 GHz FastMATH-LP processor (5.5W typ) for maximum performance per watt

#### Matrix and Vector Math Processing Unit

- · Single-instruction, multiple-data (SIMD) architecture

- 4 x 4 array of 32-bit processing elements each with local register file

- Fixed-point matrix, vector, and scalar data types

- Single-cycle full matrix load from L2 cache (zero-cycle latency, two-cycle throughput)

- 64 GOPS (peak) at 2 GHz

- 551.000 radix-4 1024-point 16-bit FFTs/sec at 2 GHz

- 32 GMACs/sec at 2 GHz

# On-chip MIPS32™ CPU

- Dual-issue core (scalar CPU + matrix math unit)

- Dual 16 Kbyte L1 caches

- · Zero load-to-use penalty

- MMU with 16 dual-entry fully associative TLB

# **DDR Memory Controller**

- Directly supports up to 1 GB of SDRAM with a 64-bit wide bus

- Speeds up to DDR-400 with ECC protection

# Large L2 Cache

- 1 Mbyte on-chip L2 cache

- 4-way set-associative architecture

- Parity protection

- Configurable as cache or SRAM in 256 Kbyte increments with no speed penalty

# Dual RapidIO™ Ports

- Fully compliant with the industry standard RapidIO specification

- 8-bit at 500 MHz clock rate

- Aggregate throughput 4 Gbytes/s

- Memory mapped and messaging protocols

- Leverages an expanding infrastructure of RapidIO support devices

# General Purpose I/O & Memory Interface

- Glueless interface to boot ROM, flash, SRAM, fast peripherals, ASICs, and FPGAs

- 8-bit or 32-bit wide bus operates up to 66 MHz

- Supports multiplexed or non-multiplexed operation

# **DMA Unit**

- · Sophisticated two-channel DMA

- · Memory-resident descriptor-based

- Features for multiprocessor interlocking and global shared memory operation

- · Multiple transfer styles supported, including striding

# **EJTAG Debug Interface**

Industry standard rev 2.6 support

# 2 GHz FastMATH™ and 1 GHz FastMATH-LP™ Adaptive Signal Processors™ Products

# TARGET APPLICATIONS

# Wireless Infrastructure

- · Cellular basestations

- Coverage and capacity enhancing applications such as multi-user detection (MUD) and smart antenna systems

- · Point-to-point & point-to-multipoint fixed wireless

### **Imaging**

- Medical (ultrasound, CT, MRI, x-ray, nuclear)

- · Machine vision

- Radar/sonar

- · Satellite imaging

- · High-end hard-copy imaging

# Military Signal Processing

# THE FastMATH ADVANTAGE

- · ASIC/FPGA performance with the flexibility and time-tomarket advantages of an embedded processor

- The FastMATH-LP device offers the highest performance per watt of any infrastruture-class embedded processor

- · Large on-chip caches are ideal for high-speed access to large data sets such as matrixes

- · Dual 8-bit RapidIO Port interfaces offer high bandwidth with low pin-count, facilitating easy system integration and flexible multiprocessor system configurations

- DMA reduces CPU burden by providing sophisticated queuing, striding, and alternate master synchronization

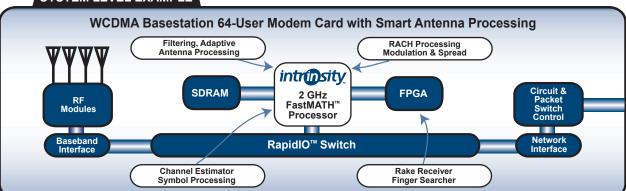

# SYSTEM LEVEL EXAMPLE

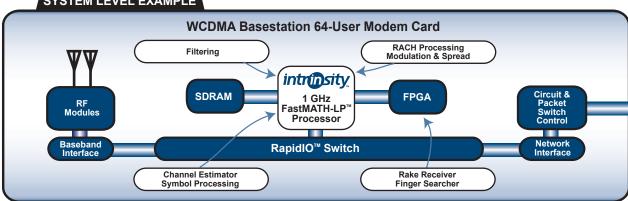

# SYSTEM LEVEL EXAMPLE

For more information please contact us at:

Email: bizdev@intrinsity.com

Phone: 512-421-2100

Intrinsity, the Intrinsity logo, Fast<sub>14</sub>, FastMATH-LP, Adaptive Signal Processor, the Faster processor company, FastMATH,and ION Ring are trademarks/registered trademarks of Intrinsity, Inc. in the United States and/or other countries. MIPS and MIPS32 are trademarks/registered trademarks of MIPS Technologies, Inc. RapidIO is a trademark/registered trademark of the RapidIO Trade Association.

# Visit our web site at: www.intrinsity.com

# **AVAILABILITY**

- FastMATH samples (2 GHz and 1.5 GHz) available today FastMATH-LP (1 GHz) samples available Q4/03

- Simulator, SDK, and evaluation platform with tools, firmware, and drivers available today

- · Additional details and specifications available upon request

intrinsity 11612 Bee Caves Road · Building II, Suite 200 · Austin, TX 78738